Flow control은 네트워크 자원, 즉 channel bandwidth, buffer capacity, control state를 네트워크를 통해 전달되는 패킷에 어떻게 할당할지를 결정한다. 효과적인 flow-control 방식은 이 자원들을 효율적으로 할당하여 네트워크가 이상적인 bandwidth의 높은 비율을 달성하고, 낮고 예측 가능한 latency로 패킷을 전달할 수 있도록 한다. 반면, 비효율적인 flow-control 방식은 일부 자원을 유휴 상태로 방치하거나 다른 자원으로 비생산적인 작업을 하여 bandwidth를 낭비한다. 이런 경우, 제2장에서 다룬 것처럼, 네트워크는 이상적인 bandwidth의 극히 일부분만을 활용하며, latency도 높고 변동성이 크다.

Flow control은 자원 할당 문제 또는 경쟁 해결 문제로 볼 수 있다. 자원 할당 관점에서 보면, 패킷이 source에서 destination으로 진행하면서 channel, buffer, state 등의 자원이 할당되어야 한다. 같은 과정을 경쟁 해결 관점에서 보면, 예를 들어 두 개의 패킷이 같은 시간에 라우터의 서로 다른 입력에서 도착하여 동일한 출력을 요구할 때, flow-control 메커니즘은 경쟁을 해결하고 해당 channel을 하나의 패킷에 할당하며, 나머지 차단된 패킷은 다른 방식으로 처리한다.

가장 단순한 flow-control 메커니즘은 bufferless이며, 차단된 패킷을 임시 저장하는 대신 드롭(drop)하거나 잘못된 경로로 전송(misroute)한다. 그보다 조금 더 복잡하고 효율적인 방식은 circuit switching으로, 여기서는 패킷 헤더만 buffering한다. circuit switching에서는 패킷의 헤더가 payload보다 먼저 네트워크를 통과하며, 경로 상의 자원을 예약한다. 특정 노드에서 자원이 즉시 할당되지 않으면, 헤더는 해당 자원이 사용 가능해질 때까지 대기한다. 전체 경로(회로)가 예약되면 데이터를 전송할 수 있고, 사용 후에는 채널을 해제하여 회로를 종료한다. 이들 flow-control 메커니즘은 상대적으로 저렴한 저장 공간 사용을 피하려다 비싼 channel bandwidth를 낭비하기 때문에 효율성이 떨어진다.

더 효율적인 flow control은 네트워크 자원이 사용 가능해질 때까지 데이터를 buffering하여 달성할 수 있다. buffering은 인접한 채널 간의 자원 할당을 시간적으로 분리(decouple)시켜 제약을 줄이고 효율성을 높인다. buffering은 store-and-forward나 cut-through flow control처럼 packet 단위로 이루어질 수도 있고, wormhole 또는 virtual-channel flow control처럼 더 미세한 단위인 flit 단위로 이루어질 수도 있다. 큰 크기의 가변 길이 패킷을 고정 크기의 작은 flit으로 나누면, 각 노드에서 필요한 저장 공간을 크게 줄일 수 있다. 또한 flit 단위로 자원을 할당하면, 하나의 physical channel 위에 여러 개의 virtual channel을 구현하기가 쉬워져 blocking을 줄이고 throughput을 향상시킬 수 있다.

이번 장에서는 flow-control 문제(섹션 12.1), bufferless flow control(섹션 12.2), circuit switching(섹션 12.3)을 순서대로 다룬다. 이어지는 13장에서는 buffered flow-control 방식들을 설명한다. 이 두 장에서는 네트워크 내 자원의 할당에만 초점을 맞춘다. 14장에서 보듯이, deadlock-free 네트워크를 유지하기 위한 추가적인 제약 조건이 있으며, 또한 endpoint에서의 buffer memory 관리와 같은 자원 관리 문제, 즉 end-to-end flow control도 존재한다. 이들은 유사한 원리를 따르지만 본 장에서는 다루지 않는다.

12.1 자원과 할당 단위

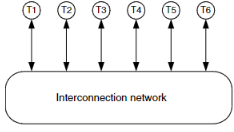

인터커넥션 네트워크를 통과하기 위해서는 message가 channel bandwidth, buffer capacity, control state와 같은 자원을 할당받아야 한다. 그림 12.1은 하나의 네트워크 노드 내에서 이러한 자원들을 보여준다. 패킷이 노드에 도착하면 우선 control state가 할당되어야 한다. flow control 방식에 따라, channel당 하나의 control state만 존재할 수도 있고, 입력이 여러 패킷에 공유될 수 있다면 여러 개의 state가 존재할 수도 있다. control state는 패킷이 해당 노드 내에서 할당받은 자원과 노드 내 이동 상태를 추적한다. 다음 노드로 이동하기 위해서는 해당 노드의 출력 채널(output channel)에서 bandwidth를 할당받아야 한다. 일부 네트워크에서는 forward channel과 함께 반대 방향으로 흐르는 reverse channel의 bandwidth도 함께 할당된다. reverse channel은 일반적으로 acknowledgment나 flow-control 정보를 전달하는 데 사용된다. 또한 패킷이 노드에 도착하면 channel bandwidth가 사용 가능해질 때까지 buffer에 임시로 저장된다. 모든 flow-control 방식은 control state와 channel bandwidth의 할당을 포함하며, 일부 방식에서는 buffer 할당은 포함하지 않는다(12.2절에서 다룸).

그림 12.1

네트워크 노드 내 자원 할당

- Control state: 패킷의 channel/buffer 할당과 노드 내 진행 상태를 기록

- Channel bandwidth: flit을 다음 노드로 전송

- Buffers: channel bandwidth를 기다리는 동안 flit을 보관

자원 할당의 효율성을 높이기 위해, message를 control state 할당 단위인 packet으로 나누고, channel bandwidth 및 buffer capacity 할당 단위인 flit으로 다시 나눈다.

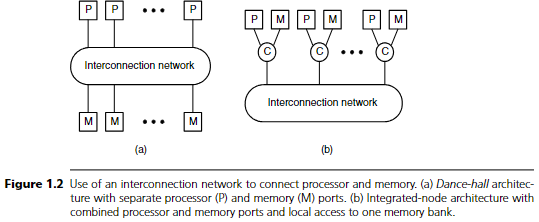

그림 12.2는 네트워크 자원이 할당되는 단위를 보여준다. 가장 상위의 message는 source terminal에서 destination terminal로 전달되는 논리적으로 연속된 비트 그룹이다. message는 길이가 임의적이므로 직접 자원이 할당되지는 않으며, 대신 길이가 제한된 하나 이상의 packet으로 나뉜다. packet의 길이를 제한하면 자원 할당의 크기와 지속 시간도 제한되며, 이는 flow control 메커니즘의 성능과 기능성 측면에서 중요하다.

packet은 routing 및 순서 지정의 기본 단위이다. packet 단위로 control state가 할당된다. 그림 12.2에서 보이듯이 packet은 message의 일부에 packet header가 앞에 붙어 구성된다. packet header는 routing information(RI)과 필요 시 sequence number(SN)를 포함한다. RI는 source에서 destination까지 패킷의 경로를 결정하는 데 사용되며, 이는 목적지 필드나 source route 등 다양한 형태일 수 있다(8장에서 설명됨). 패킷이 순서를 잃을 수 있는 경우에는 SN이 필요하다. 예를 들어, 서로 다른 경로를 통해 전달되는 경우가 이에 해당한다. 순서가 보장된다면 SN은 필요하지 않다.

packet은 다시 flow control digit 또는 flit으로 나뉜다. flit은 대부분의 flow control 방식에서 bandwidth 및 storage 할당의 기본 단위이다. flit은 routing 및 sequencing 정보를 포함하지 않으며, 따라서 같은 경로를 따라 순서를 유지해야 한다. 하지만 여러 개의 패킷이 하나의 physical channel을 통해 동시에 전송될 수 있는 시스템에서는 flit이 virtual-channel identifier(VCID)를 포함할 수 있다. 이는 flit이 어떤 packet에 속하는지를 나타낸다.

flit의 위치에 따라 head flit, body flit, tail flit, 또는 이들의 조합이 될 수 있다. head flit은 packet의 첫 번째 flit이며 routing 정보를 포함한다. 이후에 0개 이상의 body flit과 tail flit이 뒤따른다. 매우 짧은 packet의 경우 body flit이 없을 수 있으며, 극단적으로는 단일 flit로 이루어진 packet의 경우 head flit이 tail flit 역할도 한다. 패킷이 네트워크를 통과할 때 head flit은 해당 패킷을 위한 channel state를 할당하며, tail flit은 이를 해제한다. body와 tail flit은 routing이나 sequencing 정보를 가지지 않기 때문에 head flit을 따라가며 순서를 유지해야 한다.

flit은 다시 하나 이상의 phit(physical transfer digit)으로 나뉜다. phit은 한 클록 사이클 동안 channel을 통해 전송되는 정보의 최소 단위이다. 자원이 phit 단위로 할당되지는 않지만, link level protocol은 channel 상의 phit을 해석하여 flit의 경계를 파악해야 한다.

왜 flit으로 packet을 나누는가? 모든 자원 할당(channel state, buffer capacity, channel bandwidth)을 packet 단위로 할 수도 있다. 실제로 이 방식을 사용하는 flow control 정책들도 있다. 하지만 이들은 packet 크기 선택에 있어 상충되는 제약을 겪는다.

패킷 크기를 키우면 routing 및 sequencing에 드는 overhead를 분산할 수 있다. 반면, 패킷 크기를 작게 하면 자원을 더 세밀하게 효율적으로 할당할 수 있고 blocking latency를 줄일 수 있다. flit을 도입하면 이러한 상충을 제거할 수 있다. 패킷은 비교적 크게 유지하면서도 flit을 매우 작게 만들어 자원을 효율적으로 사용할 수 있다.

크기에 대한 명확한 규칙은 없지만, 일반적으로 phit은 1비트에서 64비트 사이이며, 보통 8비트이다. flit은 보통 16비트(2바이트)에서 512비트(64바이트) 사이이고, 일반적으로 64비트(8바이트)이다. packet은 보통 128비트(16바이트)에서 512킬로비트(64킬로바이트) 사이이며, 보통은 1킬로비트(128바이트)이다. 이러한 일반적인 크기를 기준으로 할 때, 하나의 64비트 flit은 8개의 8비트 phit으로 구성되고, 하나의 1킬로비트 packet은 16개의 64비트 flit으로 구성된다.

12.2 Bufferless Flow Control

가장 단순한 형태의 flow control은 buffering 없이 작동하며, channel state와 bandwidth만 경쟁하는 패킷에 할당한다. 이 경우 flow-control 방식은 arbitration을 수행하여 어떤 패킷이 요청한 채널을 사용할지를 결정해야 한다. arbitration 이후, 선택된 패킷이 해당 채널을 통해 전진한다. 이때 실패한 패킷은 buffering이 없기 때문에 보류할 수 없으며, 드롭(drop)하거나 잘못된 경로로 전송(misroute)해야 한다.

예를 들어, 그림 12.3(a)의 상황을 보자. 두 개의 패킷 A와 B가 bufferless 네트워크 노드에 도착하여 둘 다 출력 채널 0을 요청한다. 그림 12.3(b)는 드롭 방식의 flow control로 이 충돌을 처리하는 방식을 보여준다. 여기서는 A가 arbitration에서 승리하여 출력 링크를 통해 전진하고, B는 패배하여 폐기된다. 이때 B를 이 지점까지 전진시키는 데 사용된 channel bandwidth 등의 자원은 낭비된다. B는 source에서 다시 전송되어야 하며, 이 source는 B의 buffered 복사본을 갖고 있어야 한다고 가정한다. 또한, B가 성공적으로 수신되었는지 또는 재전송이 필요한지를 알려주는 acknowledgment 메커니즘도 필요하다. 대안으로, 그림 12.3(c)처럼 B를 다른 출력 채널로 misroute할 수도 있다. 이 경우에는 충분한 경로 다양성과 목적지까지 재경로 지정할 수 있는 라우팅 메커니즘이 필요하다.

그림 12.4는 그림 12.3(b)의 드롭 방식 flow control에 대해 explicit negative acknowledgment(NACK)를 사용하는 time-space 다이어그램이다. 이 도표는 Gantt 차트처럼 수직 축에는 자원(채널)의 사용을, 수평 축에는 시간을 나타낸다. 다이어그램에서는 5-flit 패킷이 4-hop 경로를 따라 전송되는 과정을 보여준다. 수직축에는 네 개 채널(03)의 forward(F) 및 reverse(R) 방향이 교차로 표시되고, 수평축은 flit cycle(017)을 나타낸다. 첫 번째 전송에서 패킷은 채널 3을 할당받지 못해 드롭되며, 이로 인해 NACK가 reverse 채널을 통해 source로 전달되고, 그에 따라 재전송이 시작된다.

패킷 전송은 cycle 0에서 head flit(H)이 채널 0을 통과하며 시작된다. body flit(B)은 cycle 1~3에서 따라오고, tail flit(T)은 cycle 4에서 따라온다. 이 경우 tail flit은 아직 acknowledgment를 받기 전이므로 채널 0을 해제하지 않는다. cycle 1과 2에서는 head flit이 채널 1과 2를 통과하지만, 채널 3에서 경쟁에 부딪혀 할당에 실패하고 드롭된다. 이 실패를 알리기 위해, 채널 2의 반대편 라우터가 cycle 3에서 NACK를 reverse 방향으로 보낸다. 이 NACK는 cycle 4와 5에 걸쳐 채널 1과 0의 reverse 방향을 통해 source에 도달하며, 경유하는 각 노드에서 자원을 해제시킨다.

source가 NACK를 받은 후, cycle 6에서 패킷을 재전송한다. 재전송된 패킷은 목적지까지 필요한 4개 채널을 모두 할당받아 전달된다. head flit은 cycle 9에 목적지에 도달하고, tail flit은 cycle 13에 도달한다. 이후 cycle 14에 acknowledgment(A)가 reverse 채널을 통해 전송되며, cycle 17에 source에 도착한다. acknowledgment가 도달할 때마다 해당 노드에서 자원이 해제된다.

2장에서 구현한 dropping flow control은 NACK를 사용하지 않는다. 대신 timeout을 통해 패킷이 드롭되었음을 감지한다.

그림 12.5는 이를 보여준다. 패킷은 처음 전송에서 채널 3 할당에 실패하지만, NACK 없이 채널 0~2까지는 계속 전송되고 tail flit이 통과할 때 자원을 해제한다. 따라서 채널 0, 1, 2는 각각 cycle 5, 6, 7에 해제된다.

timeout이 경과하고도 acknowledgment를 받지 못하면, source는 cycle 12에서 패킷을 재전송한다. 이 재전송은 cycle 15~19에 걸쳐 성공적으로 이루어지고, cycle 20에 acknowledgment가 전송되어 cycle 23에 도착한다. 이 방식에서는 tail flit 이후 자원이 해제되므로 acknowledgment도 reverse 채널에서 경쟁해야 하며, 경우에 따라 acknowledgment 자체가 드롭될 수도 있다. 이 경우, 비록 패킷이 정확히 수신되었더라도 재전송이 발생한다. 중복 패킷을 제거하고 정확히 한 번만 수신되도록 하기 위해 수신 측에서는 보통 sequence number 기반 메커니즘이 필요하다.

dropping flow control은 구조는 단순하지만, 나중에 드롭될 패킷에 bandwidth를 낭비하므로 매우 비효율적이다. explicit NACK 없이 dropping flow control의 throughput 계산 방법은 2장에서 다루었다.

한편, 그림 12.3(c)와 같은 misrouting은 패킷을 드롭하지는 않지만, 잘못된 방향으로 전송하여 bandwidth를 낭비한다. 어떤 경우에는 offered traffic이 임계점에 도달하면 네트워크 throughput이 오히려 감소하는 불안정성(instability)으로 이어질 수 있다. misrouting은 패킷이 잘못된 경로에서도 목적지까지 도달할 수 있도록 충분한 경로 다양성이 있는 네트워크에서만 가능하다. 예를 들어, butterfly 네트워크에서는 하나의 잘못된 hop만으로도 패킷이 도착할 수 없기 때문에 misrouting이 불가능하다. torus 같은 충분한 경로 다양성이 있는 네트워크에서는 misrouting이 가능하지만, 너무 자주 misroute되면 목적지에 가까워지지 않고 계속 순환하는 livelock 문제가 발생할 수 있다. 따라서 misrouting을 포함한 flow control 정책은 모든 패킷이 결국 전달된다는 forward progress 보장이 필수적이다.

12.3 Circuit Switching

Circuit switching은 bufferless flow control의 일종으로, 먼저 source에서 destination까지의 채널을 할당하여 circuit을 형성한 뒤, 하나 이상의 패킷을 그 위로 전송하는 방식이다. 더 이상 보낼 데이터가 없으면 circuit을 해제한다. 그림 12.6은 이 과정을 네 단계로 보여준다.

- 첫 번째 단계 (cycle 0~4): source에서 destination까지 request(R)가 전파되어 채널을 할당한다. 이 예시에서는 충돌 없이 바로 목적지까지 도달한다.

- 두 번째 단계 (cycle 6~10): circuit이 할당되면, acknowledgment(A)가 source로 되돌아온다.

- 세 번째 단계: acknowledgment가 도착하면 circuit이 완전히 설정되어 이후 별도의 제어 없이 임의 개수의 데이터를 보낼 수 있다. 예시에서는 4-flit 패킷 두 개가 전송되고, 그 사이에 idle cycle 3개씩 삽입되어 있다.

- 네 번째 단계 (cycle 26~30): 더 이상 보낼 데이터가 없으면 tail flit(T)을 전송하여 채널을 해제하고 circuit을 종료한다.

Circuit switching은 dropping flow control과 달리, request flit이 차단되면 드롭되는 것이 아니라 해당 위치에 유지된다. 그림 12.7은 그림 12.6과 동일하지만 request가 채널 3을 할당받기까지 4 cycle 동안 지연되는 예시를 보여준다. 이 기간 동안 head flit은 block되어 있으며, 채널 3의 근접 라우터에서 유지되면서 반복적으로 재-arbitrate를 수행한다.

그림 12.6 설명

5-hop 경로 상에서 두 개의 4-flit 패킷을 circuit switching으로 전송한 time-space 다이어그램이다. 경합은 없으며, tr = 1 cycle, D = 0이다. 전송은 네 단계로 이루어진다.

1단계: request(R)가 목적지까지 전파되며 각 hop에서 채널 상태를 확보한다.

2단계: request가 목적지에 도달하면, acknowledgment(A)가 reverse 채널을 따라 source로 되돌아온다.

3단계: acknowledgment가 source에 도착하면, data flit(D)이 예약된 채널을 따라 전송된다. 이 circuit이 열려 있는 동안에는 추가적인 패킷도 전송 가능하다.

4단계: tail flit(T)이 경로를 지나면서 채널을 해제한다.

channel 3에 대한 접근을 위해 head flit은 매 cycle마다 시도하며, 결국 cycle 7에서 채널 3을 획득하고 circuit 할당을 계속 진행한다. dropping flow control과 비교할 때, circuit switching의 장점은 패킷을 드롭하지 않고 자원을 낭비하지 않는다는 점이다. 각 hop에서 header를 버퍼링하기 때문에 항상 forward progress를 보장한다. 그러나 circuit switching은 latency가 크고 throughput이 낮은 단점이 있어, buffered flow control에 비해 덜 매력적일 수 있다.

그림 12.6과 12.7의 time-space diagram을 보면, circuit switching으로 하나의 패킷을 전송할 때의 zero-load latency는 다음과 같다:

(여기서 wire latency는 무시함)

- 첫 번째 항: 경로 설정 및 head flit 전송에 걸리는 시간 (경합 없음 가정)

- 두 번째 항: serialization latency

- 세 번째 항: 전파 시간(time of flight)

- 마지막 항: 경합 시간

이 식은 식 3.11에서 주어진 header latency의 3배가 되는데, 그 이유는 source에서 destination까지 경로를 세 번 통과해야 하기 때문이다. (회로 설정 요청, acknowledgment, 실제 데이터 전송)

그림 12.7 설명

경합이 존재하는 circuit switching의 time-space 다이어그램. 그림 12.6과 동일한 상황이지만, request가 cycle 3~6 동안 block되다가 cycle 7에서야 channel 3을 할당받는다.

이러한 세 번의 경로 통과는 짧은 패킷 하나만 전송하는 경우 latency에 큰 영향을 준다.

또한 throughput도 낮아지는데, 이유는 채널이 예약된 시간이 실제 데이터가 전송되는 시간보다 길기 때문이다. 예를 들어 단일 패킷이 전송될 경우, 각 채널은 다음과 같은 시간 동안 점유된다:

- setup 시간 2Htr 동안 채널은 유휴 상태이다.

- 이 시간 동안 다른 회로에 할당될 수도 없고, 현재 회로도 아직 데이터를 보내지 못하므로 bandwidth 낭비가 발생한다.

- 특히 단기간의 회로에서는 이 오버헤드가 상당히 크다.

Circuit switching의 장점은 매우 간단하게 구현 가능하다는 것이다.

라우터의 로직은 2장에서 설명한 dropping flow control 라우터와 거의 유사하며,

- 각 입력에 request를 유지하기 위한 레지스터와

- reverse 경로만 추가하면 된다.

12.4 참고 문헌 메모 (Bibliographic Notes)

- Circuit switching은 전화망에서 기원하였으나, 현대의 인터커넥션 네트워크에서는 흔히 사용되지 않는다.

- Dropping flow control은 비효율적이지만 단순하여, BBN Butterfly(섹션 4.5)와 그 후속 모델인 BBN Monarch(섹션 23.4)에서 사용되었다.

- Misrouting (deflection 또는 hot-potato routing이라고도 함)은 Baran[12]에 의해 소개되었고, HEP Multiprocessor[174]와 Tera Computer System[9]에서 사용되었다.

12.5 연습문제

12.1 Dropping flow control with explicit nacks

섹션 12.2 및 그림 12.4에서 설명한 explicit NACK을 사용하는 dropping flow control 방식에 대해, 네트워크 throughput의 최대 상한(용량의 비율로)을 구하라. 최대 패킷 길이는 F flits, 평균 hop 수는 H_avg, uniform 트래픽, 대칭 토폴로지를 가정하라.

12.2 Timeout interval for dropping flow control

섹션 12.2 및 그림 12.5에서 설명한 timeout을 사용하는 dropping flow control 방식에 대해, 최대 패킷 길이가 F flits이고 네트워크의 각 hop이 하나의 flit 시간(cycle)을 요구한다고 할 때, 최소 timeout 간격을 F, 네트워크 diameter를 이용하여 표현하라.

12.3 Livelock with dropping flow control and timeout

timeout 기반 dropping flow control에서는 acknowledgment를 위한 reverse 채널이 예약되지 않으므로, acknowledgment도 경합으로 인해 드롭될 수 있다. 이로 인해 발생할 수 있는 livelock 문제를 설명하고, 간단한 해결책을 제안하라.

12.4 Optimistic circuit switching

optimistic circuit switching 기법은 header와 함께 데이터를 speculative하게 전송함으로써 zero-load latency를 줄일 수 있다. 만약 header가 차단되면, 데이터는 드롭되고 NACK이 부분적으로 예약된 경로를 따라 되돌아간다. 반대로 header가 성공하면, 데이터는 회로가 설정되자마자 목적지에 도달한다. speculative 데이터가 드롭되는 경우와 그렇지 않은 경우 각각에 대해 time-space 다이어그램을 그려라. tr = 1 cycle, D = 0으로 가정한다. 이 방식이 idle 상태의 예약 채널을 줄일 수 있는가? 그렇다면 얼마나 줄일 수 있는가?

12.5 Reservation circuit switching

기존 circuit switching과 유사하지만, request 메시지가 각 채널을 미래의 일정 시간 동안 (예: 15 cycle 후부터 10 cycle 동안) 예약하는 방식의 flow control을 생각하자. 경로상의 각 라우터는 request가 수용 가능할 경우 예약을 수행한다. 만약 불가능하다면 NACK을 보내 연결을 위한 기존 예약을 모두 취소하고 다시 시도한다. request가 목적지까지 도달하면, acknowledgment가 source로 전송되어 모든 예약을 확정한다. reservation circuit switching이 기존 방식보다 유리함을 보여주는 상황의 time-space 다이어그램을 그려라.

'System-on-Chip Design > NoC' 카테고리의 다른 글

| Deadlock and Livelock (2) | 2025.06.05 |

|---|---|

| Buffered Flow Control (1) | 2025.06.05 |

| Routing Mechanics (2) | 2025.06.02 |

| Adaptive Routing (1) | 2025.06.02 |

| Oblivious Routing (3) | 2025.06.02 |