반응형

저전력 IP 설계

개요

이 장에서는 프로세서, DSP, USB, PCI Express, 버스 인프라와 같은 복잡한 IP 설계 시 저전력 설계 방법을 다룹니다. 다양한 애플리케이션에 맞게 IP를 설계하려면 아래와 같은 저전력 기술이 필요합니다:

- 전력 게이팅을 위한 설계 분할

- 전력 게이팅 지원

- 전력 의도 파일 작성

- 저전력에 맞는 클럭 및 리셋 전략

- 저전력 지원 IP 패키징

- 다양한 저전력 전략을 통한 검증

8.1 전력 게이팅을 위한 아키텍처와 분할

8.1.1 전원 차단 시점

- CPU: 소프트웨어 제어로 전력 차단, 인터럽트로 다시 활성화

- USB OTG: USB 버스가 3ms 동안 비활성화될 때 전력 차단

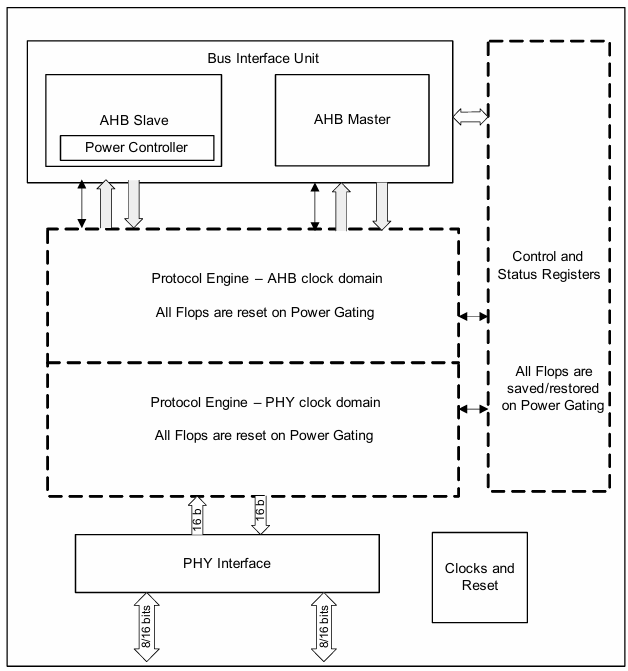

8.1.2 차단 및 유지할 블록 결정

- 유지: 버스 인터페이스, PHY 인터페이스, 클럭 및 리셋 블록

- 차단: 프로토콜 엔진, 제어 및 상태 레지스터

8.2 USB OTG의 전력 컨트롤러 설계

컨트롤 신호:

- pwr_reset_n: 리셋 제어

- gate_hclk: AHB 클럭 제어

- h2pd_stop_pclk: PHY 클럭 제어

입력 신호:

- pwr_dwn_ack_n: 전력 차단 확인

- fifo_flushed: FIFO 비움 확인

- enable_power_gating: 전력 게이팅 허용

전력 차단 절차:

- FIFO 비움 확인

- 출력 클램프 활성화

- 클럭 정지

- 레지스터 상태 저장

- 리셋 활성화

- 전력 차단 요청 및 확인

전력 복구 절차:

- 전력 공급 재개

- 리셋 해제

- 레지스터 상태 복원

- 클럭 활성화

- 출력 클램프 해제

8.3 휴대성이 있는 전력 컨트롤러 설계 이슈

- 8.3.1 다양한 라이브러리 지원

- 신호 극성 변화: IP가 사용되는 환경에 따라 신호의 극성이 달라질 수 있습니다.

- 요청/확인 핸드셰이크: 일부 라이브러리에서는 요청/확인 신호가 필요하지 않을 수 있으므로 이를 파라미터화하여 선택적으로 활성화할 수 있게 합니다.

- 저장/복구 제어: 단일 신호로 처리할지, 저장 및 복구 신호를 분리할지 선택할 수 있어야 합니다.

- 전력 게이팅이 일반화되면 여러 블록의 전력 관리를 중앙에서 제어할 필요가 있습니다.

- 동시 전력 복구 방지: 다수의 블록이 동시에 전력 복구를 시도하면 전원 노이즈가 발생할 수 있으므로 이를 시퀀싱해야 합니다.

- 중앙 전력 컨트롤러 연계: IP가 중앙 전력 컨트롤러와 소통할 수 있도록 상위 포트에 전력 요청 및 확인 신호를 노출해야 합니다.

- 라이브러리 변경 시 유연성: IP를 다양한 환경에서 재사용할 수 있도록 신호 극성, 핸드셰이크 방식 등을 파라미터로 정의합니다.

- 전력 컨트롤러 모듈화: 전력 컨트롤러를 별도 모듈로 구현하여 변경 시 IP의 나머지 부분을 수정할 필요가 없도록 설계합니다.

8.4 클럭 및 리셋 관리

- 8.4.1 클럭 관리 전략

- 클럭 게이팅: 회로의 특정 부분이 유휴 상태일 때 클럭 공급을 중단하여 전력을 절약합니다.

- 스캔 테스트 클럭 분리: 테스트 시에는 스캔 클럭을, 운영 시에는 동작 클럭을 사용하도록 클럭을 다중화합니다.

- 도메인별 독립 클럭 관리: 여러 클럭 도메인을 사용할 경우 도메인 간 클럭 간섭을 최소화하도록 설계합니다.

- 조건부 리셋: 전력 게이팅 시 리셋을 유연하게 관리하여 불필요한 상태 초기화를 방지합니다.

- 스캔 모드 리셋: 스캔 테스트 시에는 시스템 리셋 대신 테스트를 위한 별도 리셋 신호를 사용합니다.

- 도메인 간 리셋 동기화: 서로 다른 클럭 도메인 간 리셋 신호를 전달할 때 동기화 회로를 통해 메타스테이블 상태를 방지합니다.

- 모듈화된 설계: 클럭 및 리셋 회로를 별도 모듈로 분리하여 유지보수를 용이하게 합니다.

- 전력 컨트롤러 연동: 전력 컨트롤러와의 인터페이스를 통해 전력 게이팅 시 클럭과 리셋이 올바르게 동작하도록 설계합니다.

- 저전력 IP 설계에서는 클럭 및 리셋 신호의 효율적 관리가 필수적입니다. 클럭이 불필요하게 동작하면 전력 소모가 증가하고, 불필요한 리셋은 시스템 안정성을 저하시킬 수 있습니다. 이를 위해 다음과 같은 전략을 적용합니다:

- 전력 컨트롤러의 설계는 다양한 라이브러리와 시스템 환경에 맞춰야 하므로, 다음과 같은 이슈를 고려해야 합니다:

8.5 검증

- 전력 게이팅 전후로 기능 테스트

- RTL 시뮬레이션과 게이트 레벨 시뮬레이션 수행

8.6 전력 의도를 고려한 IP 패키징

- IP 구성 툴을 통해 전력 컨트롤러, 테스트 벤치, 전력 의도 설정 지원

8.7 USB OTG 코어의 UPF 코드 예제

- UPF를 통해 전력 게이팅, 클램프, 레지스터 유지 기능을 정의

8.8 USB OTG 전력 컨트롤러의 상태 머신

- 상태: 대기, 전력 차단, 복구

- 절차: 클램프->클럭 차단->저장->전력 차단 및 복구 시 반대 순서로 진행

이와 같은 설계 방법을 통해 다양한 애플리케이션에서 유연하고 효율적인 저전력 IP를 구현할 수 있습니다.

반응형

'IT' 카테고리의 다른 글

| DVFS 설계 (0) | 2025.02.14 |

|---|---|

| Frequency and Voltage Scaling Design (1) | 2025.02.14 |

| IP Design for Low Power (0) | 2025.02.14 |

| Power Gating Architecture Issues (0) | 2025.02.14 |

| Power Gating Design (0) | 2025.02.14 |