반응형

6.1 Hierarchy and Power Gating

- 모듈 경계 명확화: 모듈은 하나의 전력 도메인에만 속하도록 설계.

- 계층적 파워 게이팅 제한: 다중 계층의 전력 스위칭은 성능 저하 및 복잡성 증가.

- 평탄화된 전력 스위칭 구조: 계층적 설계라도 구현 시에는 단일 레벨의 전력 게이팅으로 평탄화.

Recommendations:

- 전력 게이팅 영역을 모듈 경계와 일치시키기.

- 계층적 전력 게이팅을 평탄화된 스위칭 구조로 매핑.

Pitfalls:

- 전력 다운된 영역을 통과하는 제어 신호 피하기.

- 필요 이상으로 세분화된 전력 게이팅을 피하고 1~2레벨로 제한.

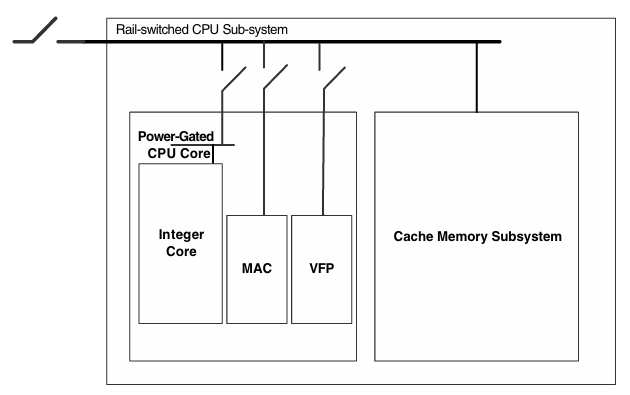

이 그림은 Rail-switched CPU Sub-system의 전력 게이팅 구조를 나타낸 것입니다. 주요 구성 요소와 전력 흐름은 다음과 같습니다:

1. 전체 구조

- 상단에 Rail-switched CPU Sub-system 전력 레일이 존재하며, CPU 서브시스템 전체에 전력을 공급합니다.

- 전력은 CPU Core 및 Cache Memory Subsystem으로 분배됩니다.

2. Power-Gated CPU Core

- Power-Gated CPU Core는 전력 게이팅 기술을 적용하여 유휴 상태일 때 전력을 차단하여 누설 전력을 줄이는 구조입니다.

- Integer Core는 항상 CPU Core 내에 존재하며, 필수적인 연산을 담당합니다.

3. MAC (Multiply-Accumulate) 및 VFP (Vector Floating Point)

- MAC과 VFP는 독립적으로 전원을 차단할 수 있는 기능을 가지고 있습니다.

- 이를 통해 필요한 연산 유닛만 활성화하여 전력 소비를 최소화할 수 있습니다.

- MAC: 행렬 연산과 누적 연산 등 DSP 관련 작업 수행.

- VFP: 벡터 부동소수점 연산을 담당하여 고속 계산 성능 지원.

전력 흐름:

- MAC이나 VFP를 사용할 때는 CPU Core 전원이 반드시 켜져 있어야 합니다.

- 이 구조는 다중 계층의 전력 스위칭을 방지하고 성능 저하를 줄이기 위한 설계입니다.

4. Cache Memory Subsystem

- Cache Memory Subsystem은 전력 게이팅 없이 독립적으로 전력이 공급됩니다.

- 이 설계는 Deep Sleep 모드에서도 캐시 데이터를 유지하기 위함입니다.

5. 전력 제어 방식

- 전력 스위치는 CPU Core, MAC, VFP 등 주요 유닛에 독립적으로 적용됩니다.

- 전력 제어는 상위 전력 레일에서 내려오는 전력을 통해 이루어집니다.

운영 모드 예시:

- Shutdown: 모든 전력을 끄고 캐시 메모리도 비움.

- Deep Sleep: CPU 코어를 끄고 캐시는 유지.

- DSP Workload: MAC을 활성화하여 DSP 작업 수행.

- Intensive Multimedia Mode: CPU, MAC, VFP 모두 활성화.

요점

- 전력 게이팅을 통해 성능과 전력 효율의 균형을 맞춘 구조.

- 계층 구조를 단순화하고 CPU Core를 중심으로 MAC, VFP를 독립적으로 제어.

- Cache Memory Subsystem은 독립적으로 전력 공급받아 데이터 유지.

6.2 Power Networks and Their Control

6.2.1 External Power Rail Switching

- CPU 전력 네트워크 예제: 캐시 보존을 위한 전력 레일, 전력 게이팅 컨트롤러를 위한 항상 켜짐(always-on) 전력 등.

- 외부 전력 스위칭 특징: 긴 전력 안정화 시간(수십~수백 μs)과 전류 급상승(in-rush current)으로 인한 노이즈 발생.

- 공통 접지 사용 권장: 전력 공급 시 공통 접지(VSS) 사용이 설계 단순화에 유리.

Recommendations:

- 외부 전력 레일 수를 최소화.

- 전압 스케일링 영역은 별도 전력 레일로 설계.

Pitfalls:

- 긴 전력 스위칭 시간(수만~수십만 클럭 사이클) 고려.

- 전력 레일 증가 시 검증 및 생산 단계 복잡성 증가.

이 다이어그램은 외부 전력 레일 스위칭(External Power Rail Switching) 구조를 보여주고 있습니다. SoC(System-on-Chip) 설계에서 누설 전력(Leakage Power)을 줄이기 위해 전력 레일을 외부에서 제어하는 구조를 설명합니다. 주요 구성 요소와 흐름은 아래와 같습니다:

1. Power Supply (좌측)

- PSU Regulator: 전압을 안정적으로 공급하는 전력 공급 장치입니다.

- PSU Regulator (with Enable): 전력 공급을 제어할 수 있는 기능이 포함되어 있습니다.

- Enable 신호를 통해 전력 공급을 켜거나 끌 수 있습니다.

- 이 두 개의 레귤레이터는 SoC로 전력을 공급하며, 필요에 따라 Rail-switched Sub-system에 전력 제공을 중단할 수 있습니다.

2. SoC 영역 (우측)

- Always-on VDDSOC Power Rail: SoC의 항상 켜져 있어야 하는 블록에 전력을 공급합니다.

- PSU Control Interface와 Isolation Cell 등에 사용됩니다.

- PSU Control Interface:

- 전력 공급 장치를 제어하며, 전력 게이팅 명령을 내립니다.

- 외부 PSU Regulator로부터 신호를 받아 전력 레일의 on/off를 결정합니다.

3. Externally Switched VDD Power Rail

- 외부 스위칭 전력 레일은 특정 Rail-switched Sub-system에 전력을 공급합니다.

- PSU Control Interface가 전력을 끄면 Rail-switched Sub-system의 전원이 차단되어 누설 전력이 줄어듭니다.

4. Rail-switched Sub-system

- CPU 서브시스템과 같은 전력 게이팅 대상 모듈입니다.

- 필요 시 전력이 공급되며, 유휴 시 전력이 차단되어 전력 소모를 최소화합니다.

5. VSS Ground Rail (하단)

- 모든 전력 공급이 공통 접지(Ground)를 공유합니다.

- 공통 접지를 통해 전력 스위칭 시 발생할 수 있는 노이즈를 최소화합니다.

전력 흐름 요약

- PSU Regulator가 VDDSOC 레일을 통해 SoC에 기본 전력 공급.

- PSU Control Interface가 필요 시 PSU Regulator(with Enable)를 활성화.

- Externally Switched VDD Power Rail을 통해 Rail-switched Sub-system에 전력 공급.

- 사용하지 않는 경우 전력 레일을 비활성화하여 누설 전력 최소화.

설계 시 고려사항

- 전력 레일 스위칭 시 발생하는 In-rush Current(초기 전류 급상승)에 따른 노이즈 관리 필요.

- 전력 안정화 시간(수십~수백 μs)을 충분히 고려하여 전력 관리 소프트웨어 설계.

- 외부 전력 레일 수는 최소화하여 복잡성 및 비용 증가 방지.

6.2.2 On-Chip Power Gating

- 칩 내 전력 게이팅: 외부 스위칭보다 빠르며, 작은 영역일수록 빠르게 게이팅 가능.

- 소규모 블록 전력 게이팅: 클럭 사이클 단위로 빠른 전력 관리 가능.

Recommendations:

- 전력 게이팅 시간(수십~수백 클럭 주기) 설계 시 고려.

- 동적 전력 게이팅 인터페이스에서 대기 상태(wait-states) 적용.

Pitfalls:

- 전력 게이팅 영역 증가 시 검증 및 테스트 복잡성 증가.

6.3 Power State Tables and Always On Regions

- 다중 전력 도메인 관리: 각 도메인 간 전력 공급 관계를 명확히 정의해야 신호 무결성 보장.

- 상대적 항상 켜짐(relatively always-on): 특정 도메인이 다른 도메인보다 오래 켜져 있을 때 해당 도메인을 항상 켜짐으로 간주.

- 전력 라우팅 규칙 복잡성: 전력 게이팅 관계에 따라 버퍼 전력 공급원 결정 필요.

UPF 활용:

- create_pst 및 add_pst_state 명령으로 전력 상태 테이블 생성하여 의존 관계 명확히 정의.

이 다이어그램은 Power-Gated 도메인 간의 신호 전달 및 아이솔레이션(Isolation) 구조를 보여줍니다. Domain A, Domain B, Domain C라는 세 개의 전력 도메인 간에 데이터가 전달되는 구조를 나타내며, 전력 게이팅과 신호 무결성을 유지하기 위한 설계 기법을 설명하고 있습니다.

구성 요소 및 동작 원리

1️⃣ Domain A (왼쪽)

- Retention Flop: 전원이 꺼져도 중요한 상태를 유지하기 위한 플롭(flop)입니다.

- Isolation Cell (Iso): Domain A가 전력 게이팅되어 꺼질 때 출력 신호를 안전한 값(예: '0')으로 고정하여, 후속 도메인(Domain B)에 잘못된 신호가 전달되지 않도록 보호합니다.

- 클럭 입력(Clock Input): 플롭의 데이터 동기화를 담당합니다.

역할:

- 전력이 꺼져도 Retention Flop이 필수 데이터를 유지.

- Domain A가 꺼질 때 Isolation Cell이 활성화되어 안정적인 신호를 전달.

2️⃣ Domain B (중간)

- 전력 게이팅 없음: Domain B는 항상 켜져 있는 도메인(Always-on Domain)으로, Domain A와 Domain C 간의 신호를 중계합니다.

- 버퍼(Buffer): 신호를 증폭하거나 안정적으로 전달하는 역할을 수행합니다.

역할:

- Domain A가 꺼지더라도 Domain B는 동작을 유지하여 신호 전달을 지원.

3️⃣ Domain C (오른쪽)

- Retention Flop: Domain C 역시 전력 게이팅이 적용되며, 중요한 데이터를 유지하기 위한 플롭이 있습니다.

- Isolation Cell (Iso): Domain C가 전력 게이팅으로 꺼질 때 입력 신호를 안정적으로 고정합니다.

역할:

- Domain C가 꺼질 경우 입력 신호를 안정화하고, 전원이 다시 켜질 때 Retention Flop을 통해 이전 상태를 복원.

동작 시나리오

- Domain A 동작 시

- 클럭이 활성화되면 Domain A의 Retention Flop이 데이터(D)를 처리하고 출력(Q)으로 전달.

- Domain A가 전력 게이팅으로 꺼지면 Isolation Cell이 활성화되어 출력 신호를 고정.

- Domain B를 통한 신호 전달

- Domain B는 항상 켜져 있어 신호를 안정적으로 Domain C로 전달.

- Domain C의 전력 게이팅

- Domain C가 켜져 있으면 정상 동작.

- Domain C가 꺼질 때는 Isolation Cell이 출력 신호를 고정하고, Retention Flop이 중요한 상태를 유지.

설계 시 고려사항

- Isolation Cell은 전력이 꺼지는 도메인 경계에 필수로 추가해야 하며, 특히 신호가 항상 켜져 있는 도메인으로 전달될 때 반드시 필요합니다.

- Retention Flop은 전력 게이팅 시에도 중요한 데이터를 유지하므로, 전력 효율성과 데이터 무결성 측면에서 매우 중요합니다.

- 신호 무결성 보장을 위해 도메인 간 클럭 도메인 크로싱(clock domain crossing)을 신중히 설계해야 합니다.

요약

- Power Gating 환경에서 신호 전달 안정성 확보를 위한 구조입니다.

- 전력이 꺼지는 도메인에는 Isolation Cell과 Retention Flop을 적용하여 **데이터 무결성(Data Integrity)**을 유지.

- 항상 켜져 있는 Domain B가 브릿지 역할을 수행하며 신호를 안정적으로 전달.

- UPF(Universal Power Format)를 활용해 이러한 전력 관계를 설계할 수 있습니다.

이 구조는 저전력 설계(Low-Power Design)에서 필수적인 기법이며, 특히 SoC 설계 시 다양한 전력 모드 전환 시에 안정성을 보장합니다. 🔋⚡

전체 요약:

- 전력 게이팅은 성능 저하를 최소화하면서 누설 전력(leakage)을 줄이기 위한 설계 기법.

- 계층적 구조는 설계 수준에서만 유지하고 구현 시에는 평탄화.

- 외부 전력 스위칭은 안정화 지연과 노이즈 문제를 고려.

- 칩 내부 전력 게이팅은 전력 및 클럭 지연을 사전에 평가.

- 다중 전력 도메인 간 의존 관계는 UPF를 사용해 명확히 정의.

반응형

'IT' 카테고리의 다른 글

| IP Design for Low Power (0) | 2025.02.14 |

|---|---|

| IP Design for Low Power (0) | 2025.02.14 |

| Power Gating Design (0) | 2025.02.14 |

| Power Gating Overview (0) | 2025.02.14 |

| Multi-Voltage Design (0) | 2025.02.14 |