반응형

표준 저전력 기법

이 문서는 저전력 설계에서 사용되는 다양한 성숙한 기술들을 설명합니다.

1. 클록 게이팅

클록 게이팅은 필요하지 않을 때 클록 신호를 비활성화하여 동적 전력 소비를 줄이는 기술입니다.

- 클록 버퍼는 동적 전력 소비의 최대 50%를 차지할 수 있습니다.

- 자동 클록 게이팅 도구는 기능 변경 없이 게이팅이 가능한 회로를 감지합니다.

- 최신 라이브러리는 합성 도구에서 인식할 수 있는 특정 클록 게이팅 셀을 제공합니다.

결과

Pokhrel의 연구에 따르면, 180nm 칩에서 클록 게이팅을 적용한 결과:

- 면적 감소: 20%

- 전력 절감: 34%-43%

- 클록 게이팅 셀을 클록 경로 초기에 배치하여 큰 전력 절감 효과를 보임.

2. 게이트 레벨 전력 최적화

게이트 레벨에서의 최적화 기법은 동적 전력을 줄이는 데 유용합니다:

- 고활성 네트워크를 재구성하여 용량 감소.

- 고활성 네트워크를 저전력 입력 핀에 연결하여 최적화.

- 셀 크기 조정 및 버퍼 삽입을 통해 타이밍과 전력 최적화.

3. 다중 VDD

다중 VDD 설계는 전력 소모를 줄이기 위해 각 기능 블록에 다른 전압을 할당합니다.

- 동적 전력은 VDD²에 비례하므로 전압을 낮추면 전력이 절감됩니다.

- 캐시 RAM은 높은 성능을 유지하기 위해 가장 높은 전압에서 동작합니다.

- 복잡한 전력 그리드 및 레벨 시프터 추가 필요.

4. 다중 임계 전압(Multi-VT) 논리

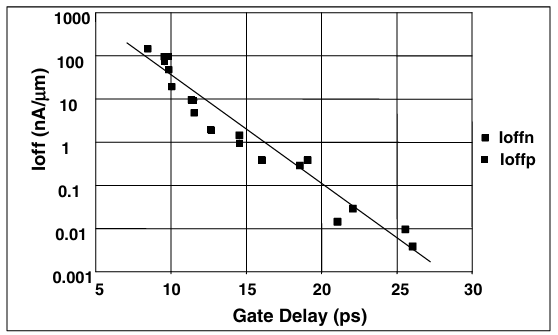

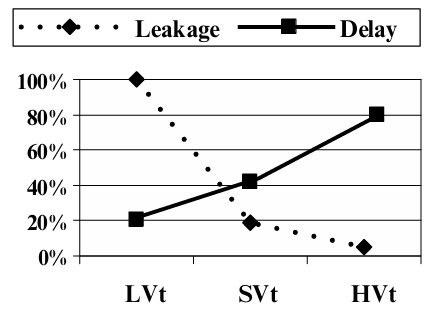

여러 임계 전압(VT) 트랜지스터를 사용하면 누설 전류를 줄일 수 있습니다:

- 고속 트랜지스터는 누설 전류가 크지만 속도가 빠름.

- 저누설 트랜지스터는 속도가 느리지만 전력 절감 가능.

- 듀얼 VT 플로우를 활용하여 타이밍과 전력을 동시에 최적화.

5. 저전력 기술 요약

| 기법 | 전력 절감 효과 | 타이밍 페널티 | 면적 페널티 | 아키텍처 영향 | 설계 영향 | 검증 영향 | 배치 및 라우팅 영향 |

|---|---|---|---|---|---|---|---|

| 클록 게이팅 | 높음 | 낮음 | 낮음 | 낮음 | 낮음 | 낮음 | 중간 |

| 게이트 레벨 최적화 | 중간 | 적음 | 없음 | 없음 | 낮음 | 낮음 | 낮음 |

| 다중 VDD | 높음 | 중간 | 중간 | 높음 | 중간 | 낮음 | 중간 |

| 다중 VT | 중간 | 적음 | 낮음 | 낮음 | 낮음 | 낮음 | 낮음 |

반응형

'IT' 카테고리의 다른 글

| Power Gating Overview (0) | 2025.02.14 |

|---|---|

| Multi-Voltage Design (0) | 2025.02.14 |

| Standard Low Power Methods (0) | 2025.02.13 |

| SoC 클럭 설계 이해 (0) | 2025.02.13 |

| SoC 클럭 기술 (0) | 2025.02.13 |