DVFS(Dynamic Voltage and Frequency Scaling)는 서브시스템의 클럭 주파수와 전원 전압을 조정하는 기법입니다.

이러한 조정은 일반적으로 저역통과 필터(low-pass filter)가 포함된 피드백 루프에 의해 제어됩니다.

즉, 클럭과 전압 조정에는 일정한 관성(inertia, 지연)이 존재하며, 변경은 최소 1~10ms 단위로 수행되어야 합니다.

추가적인 전력 절감 기법으로는 클럭 차단(clock gating)과 서브시스템의 전원 차단(power gating)이 있습니다.

이 두 방법은 디지털 방식으로 즉각적으로 실행 가능하여 매우 빠르게 적용할 수 있습니다.

여기에서는 자동 클럭 게이팅(Automatic Clock Gating)에 대해 설명합니다.

1. 클럭 분배 트리와 전력 소비

SoC(System on Chip)의 클럭 분배 트리(Clock Distribution Tree)는 SoC 내에서 상당한 양의 전력을 소비합니다. 실제로, 클럭 신호는 비활성 서브시스템에서도 전체 에너지의 약 10%를 소비할 수 있습니다. 논리 회로 영역에서 모든 플립플롭(flip-flop)이 현재의 데이터를 유지하고 있다면, 즉 클럭을 통해 새로운 데이터가 로드되지 않는다면, 해당 영역은 유휴(idle) 상태라고 할 수 있습니다. 하지만, 이러한 유휴 상태에서도 클럭이 계속 공급되면 불필요한 전력 소모가 발생하여 해당 영역은 여전히 10%의 전력을 소비하게 됩니다. 유휴 기간(idle period)은 연속된 여러 개의 유휴 클럭 사이클로 정의됩니다. 이 기간은 단 하나의 클럭 사이클에서 수천 개의 클럭 사이클까지 지속될 수 있습니다. 따라서, 유휴 상태에서 클럭을 차단하면 상당한 전력 절감 효과를 얻을 수 있습니다.

2. 클럭 게이팅 방식

2.1 클럭 게이팅 회로의 종류

그림 4.31은 서브시스템의 클럭을 비활성화하는 세 가지 회로를 보여줍니다.

(a) 비동기적 클럭 인에이블 구조 (Asynchronous Clock Enable Structure)

- 외부 멀티플렉서(Multiplexer)를 사용하여 클럭을 선택.

- 이 멀티플렉서는 실제로 플립플롭 내부에 일부로 구현됨.

- 그러나 클럭 신호 자체를 차단하지 않기 때문에 동적 전력 소모를 줄이지 못함.

(b) AND 게이트를 이용한 클럭 게이팅 (Clock Gating with AND Gate)

- 클럭 신호와 클럭 인에이블(CEN) 신호를 AND 게이트를 통해 조합.

- 문제점:

- 클럭이 HIGH 상태에서 CEN이 변하면 클럭 글리치(Glitch, 잡음)가 발생할 가능성이 있음.

(c) OR 게이트를 이용한 클럭 게이팅 (Clock Gating with OR Gate)

- OR 게이트를 사용하여 클럭 인에이블 신호를 제어.

- 문제점:

- 클럭이 LOW 상태에서 CEN이 변하면 글리치가 발생할 가능성이 있음.

3. 클럭 게이팅 시 발생하는 문제와 해결 방법

3.1 클럭 게이팅 글리치 방지

AND/OR 게이트를 사용하는 방식의 가장 큰 문제는 클럭 신호의 글리치(Glitch)입니다.

이를 해결하기 위해 투명 래치(Transparent Latch)를 사용하여 CEN 신호의 변화를 지연시킵니다.

즉, 안전한 클럭 신호 구간에서만 CEN 신호가 적용되도록 합니다.

그림 4.32에서:

- 투명 래치가 CEN 신호를 지연시켜 클럭을 안정적으로 게이팅합니다.

- 이를 통해 글리치 없이 안전한 클럭 차단이 가능해집니다.

3.2 클럭 게이팅 도메인 간의 신호 스큐 문제

- 비게이팅 도메인(non-gated domain)과 게이팅된 도메인(gated domain) 간에 신호 전송 시 클럭 스큐(clock skew)가 발생할 수 있음.

- 이러한 비정상적인 신호 경로로 인해 shoot-through(신호 전파 오류)가 발생할 가능성이 있음.

해결책:

- 딜레이 버퍼(Delay Buffer)를 삽입하여 비게이팅된 신호 경로를 조정.

4. 클럭 인에이블 조건 생성 (Clock Enable Condition Generation)

클럭을 비활성화하려면 어떤 조건에서 클럭을 차단할 것인지 정의하는 로직이 필요합니다.

4.1 소프트웨어 제어 방식

- 소프트웨어를 통해 클럭 게이팅을 제어하는 방식.

- 예: 레지스터 플래그(Register Flags)를 활용하여 특정 블록의 클럭을 제어.

- 이 방식은 전력 차단(Power Gating)에서도 일반적으로 사용됨.

4.2 자동 검출 방식 (Automatic Detection)

- 최신 설계에서는 자동 클럭 게이팅을 위한 추가적인 논리 회로를 삽입.

- 논리 합성(Synthesis) 과정에서 자동으로 추가됨.

- 클럭이 필요할 경우, 해당 레지스터 그룹에만 클럭을 공급.

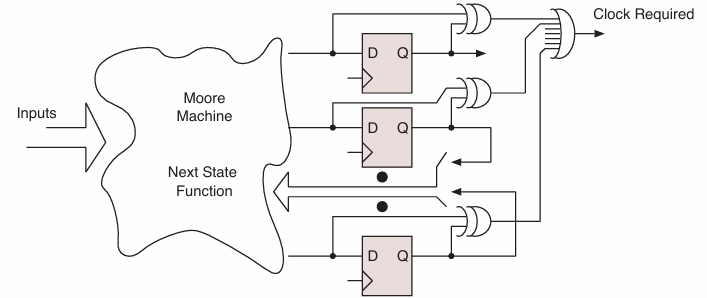

예: Mitre 패턴(Mitre Pattern)

- 플립플롭의 D 입력과 Q 출력의 차이를 비교하여 클럭이 필요한지 판단.

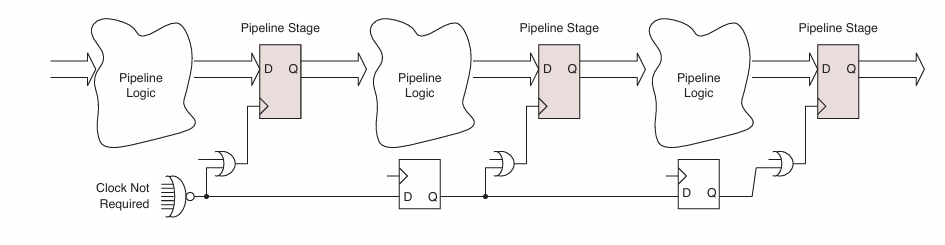

5. 파이프라인 기반 클럭 게이팅 (Pipeline Clock Gating)

파이프라인 구조에서는 한 단계(Stage)의 활동이 다음 단계(Stage)의 활동에 영향을 미칠 수 있습니다.

이를 활용하여 클럭 게이팅 영역 간 정보를 공유하면 전력 절감 효과를 극대화할 수 있습니다.

그림 4.34:

- 이전 클럭 사이클에서 활성화된 영역의 정보를 다음 클럭 사이클에서 다른 영역에서 활용.

- 필요할 때만 클럭을 공급하여 불필요한 전력 소모를 방지.

6. 결론

- 동적 클럭 게이팅(Dynamic Clock Gating)은 SoC의 전력 소비를 줄이기 위한 핵심 기술.

- 투명 래치(Transparent Latch)를 사용하여 클럭 글리치 문제를 해결.

- 자동 클럭 인에이블 검출(Auto Clock Enable Detection)을 통해 최적화.

- 파이프라인을 활용한 클럭 게이팅 정보 공유로 추가적인 전력 절감 가능.

'System-on-Chip Design' 카테고리의 다른 글

| 클럭 트리 삽입 (Clock Tree Insertion) (0) | 2025.03.01 |

|---|---|

| Clock Sources, PLL and Clock Trees (0) | 2025.03.01 |

| 시스템 반도체 설계를 위한 SysML 기반의 기능 분석 (2) | 2025.02.22 |

| SERDES(Serializer/Deserializer)의 개념, 아키텍처, 그리고 응용 분야 (2) | 2025.02.20 |

| Serdes (Serializer/Deserializer) (0) | 2025.02.20 |