SerDes(Serializer/Deserializer) 개요

SerDes(Serializer/Deserializer)는 데이터 직렬화(Serialization) 및 역직렬화(Deserialization)를 수행하는 회로 블록으로, 병렬 데이터를 직렬 데이터로 변환하거나 그 반대로 변환하는 역할을 합니다.

고속 데이터 전송이 필요한 시스템에서 널리 사용되며, 대표적으로 고속 인터페이스(PCIe, USB, SATA, Ethernet, DisplayPort, HDMI, MIPI D-PHY, C-PHY 등) 에서 활용됩니다.

1. SerDes의 동작 원리

SerDes는 기본적으로 두 가지 주요 블록으로 구성됩니다.

- Serializer (직렬화)

- 다중(병렬) 데이터를 단일 고속 직렬 데이터 스트림으로 변환

- 병렬 클럭 신호를 직렬화하여 전송 속도를 증가시킴

- 동기화 및 데이터 정렬 기능을 수행

- Deserializer (역직렬화)

- 직렬로 전송된 데이터를 다시 다중(병렬) 데이터로 변환

- 클럭 복원 기능 (Clock Recovery)을 사용하여 수신된 데이터를 동기화

- 오류 검출 및 데이터 무결성을 유지하기 위한 기능을 포함

2. SerDes의 필요성

(1) 고속 데이터 전송

- 병렬 데이터 전송 방식은 클럭 신호와 여러 데이터 라인 간의 스큐(Skew, 신호 간 지연 차이) 문제로 인해 높은 속도에서 신뢰성을 유지하기 어려움.

- 직렬화하여 단일 또는 적은 수의 신호 라인을 사용하면 신호 무결성(Signal Integrity) 이 향상되고 전송 속도를 높일 수 있음.

(2) 핀 개수 감소

- 병렬 데이터 전송을 사용하면 각 데이터 비트마다 물리적 신호 라인이 필요함.

- SerDes를 사용하면 핀 수를 줄여 패키지 크기와 PCB 설계를 단순화할 수 있음.

(3) 전력 소비 절감

- 직렬 인터페이스는 병렬 인터페이스보다 전력 소모가 낮아 저전력 설계에 유리.

3. SerDes의 주요 기술 요소

(1) 직렬화 기법

- 멀티플렉싱(Multiplexing) : 여러 개의 저속 병렬 신호를 하나의 고속 직렬 신호로 변환

- 8b/10b Encoding, 64b/66b Encoding : DC 밸런스 유지 및 클럭 복원을 용이하게 함

(2) 클럭 데이터 복원 (Clock Data Recovery, CDR)

- 직렬 데이터에서 클럭 정보를 복원하여 안정적인 데이터 복구

- PLL(Phase-Locked Loop) 또는 DLL(Delay-Locked Loop) 을 사용하여 타이밍 동기화

(3) Equalization (등화)

- 고속 전송에서 발생하는 ISI (Inter-Symbol Interference) 를 보정하기 위해 사용

- TX Pre-emphasis, RX Equalization, DFE(Decision Feedback Equalizer) 등의 기술 사용

(4) 오류 검출 및 보정

- CRC (Cyclic Redundancy Check), ECC (Error Correction Code), Scrambling 기법을 사용하여 신호 무결성을 유지

4. SerDes의 응용 분야

인터페이스설명

| PCIe | 고속 컴퓨터 버스, GPU, SSD, 네트워크 카드 등에 사용 |

| SATA | SSD 및 HDD의 데이터 전송 인터페이스 |

| USB 3.x/4.0 | 고속 데이터 및 영상 전송 |

| Ethernet (10G, 25G, 100G, 400G) | 네트워크 장비, 서버, 데이터센터 |

| DisplayPort, HDMI | 디지털 영상 전송 인터페이스 |

| MIPI D-PHY, C-PHY | 모바일 카메라 및 디스플레이 인터페이스 |

| Thunderbolt | 초고속 데이터 및 디스플레이 인터페이스 |

5. SerDes의 신호 무결성 고려 사항

SerDes는 고속 신호를 전송하는 만큼 신호 무결성(Signal Integrity, SI) 이 중요합니다. 주요 고려 사항은 다음과 같습니다.

- 지터(Jitter) 관리

- 클럭 변동으로 인해 데이터 샘플링 오류 발생 가능 → PLL 및 CDR을 활용하여 보정

- 신호 감쇠(Attenuation)

- PCB 트레이스에서 신호 감쇠 발생 → TX Pre-emphasis 및 RX Equalization 사용

- 반사(Reflection)

- 임피던스 불일치로 인해 반사 발생 → PCB 설계 시 임피던스를 매칭해야 함

- 노이즈 및 EMI (Electromagnetic Interference)

- 차폐(Shielding) 및 필터링 기법 적용 필요

6. SerDes 설계 시 고려해야 할 사항

- 채널 손실 (Channel Loss): 신호 경로에서 발생하는 손실을 최소화하기 위해 최적의 PCB 레이아웃 설계 필요

- Tx와 Rx 간 Eye Diagram 확인: Eye Opening이 작아지면 데이터 복구가 어려워지므로 충분한 Eye Margin 확보 필요

- Pre-Emphasis 및 Equalization 조정: 채널 특성에 맞춰 최적화해야 함

7. 결론

SerDes는 고속 데이터 전송을 위해 필수적인 기술로, 다양한 인터페이스(PCIe, USB, Ethernet, SATA, HDMI, MIPI 등)에서 사용됩니다.

신호 무결성 및 전력 효율성을 높이기 위해 클럭 복원, 등화(Equalization), 오류 검출 및 보정 기법이 필수적으로 사용됩니다.

SerDes를 활용한 설계에서는 채널 손실, 지터, 반사 등 신호 무결성을 고려한 설계가 필수적입니다.

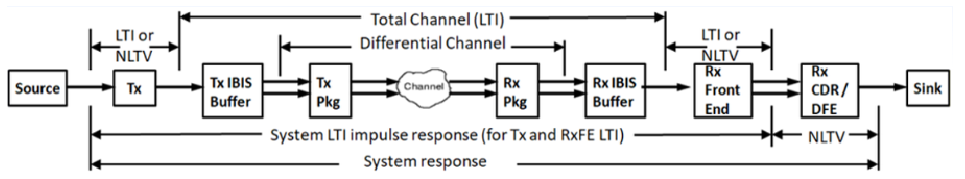

위의 그림은 SerDes(Serializer/Deserializer) 신호 경로를 나타내며, 고속 직렬 데이터가 송신(Source)에서 수신(Sink)으로 전달되는 과정에서의 주요 구성 요소들을 보여줍니다.

1. 블록별 설명

(1) Source (송신 데이터)

- 데이터를 생성하는 원천(Source)입니다.

- 일반적으로 고속 직렬 데이터를 생성하는 디지털 회로(예: 프로세서, FPGA, ASIC 등)에서 신호를 생성합니다.

(2) Tx (Transmitter, 송신기)

- 병렬 데이터를 직렬 데이터로 변환(Serialization) 하는 역할을 합니다.

- 신호 증폭, pre-emphasis(사전 강조) 및 드라이버 기능을 수행합니다.

- LTI(Linear Time-Invariant) 또는 NLTV (Non-Linear Time-Variant) 동작이 가능함.

(3) Tx IBIS Buffer

- IBIS(Input/Output Buffer Information Specification) 모델을 사용하여 송신기의 입출력 특성을 모델링합니다.

- IBIS 모델을 기반으로 전압 스윙, 드라이버 특성, 패키지 임피던스 등을 고려하여 신호가 전송됩니다.

(4) Tx Package (Tx Pkg)

- 송신기와 채널 사이의 신호 연결을 담당하는 패키지입니다.

- PCB에서 사용되는 인터포저, 본딩 와이어, BGA(Ball Grid Array) 등의 영향을 포함할 수 있습니다.

- 높은 주파수에서 패키지 손실, 반사 및 지터(Jitter) 가 발생할 수 있으므로 신호 무결성을 고려해야 합니다.

(5) Channel (전송 채널)

- 신호가 물리적으로 전달되는 배선이나 PCB 트레이스, 케이블 등의 경로입니다.

- 차동 신호(Differential Signaling) 및 LTI(Linear Time-Invariant) 모델을 기반으로 동작합니다.

- 고속 신호 전송 시 신호 감쇠(Attenuation), ISI(Inter-Symbol Interference), 반사(Reflection), EMI(Electromagnetic Interference) 등의 영향을 받습니다.

(6) Rx Package (Rx Pkg)

- 수신기 패키지로, 신호를 IC 내부로 전달하기 위한 물리적 인터페이스입니다.

- Tx Package와 마찬가지로 신호 손실 및 반사가 발생할 수 있습니다.

(7) Rx IBIS Buffer

- Rx(수신기)의 IBIS 모델을 적용하여 신호 복구 및 버퍼링을 수행합니다.

- 신호 무결성(Signal Integrity)을 유지하고 노이즈를 최소화하는 역할을 합니다.

(8) Rx Front End

- 신호를 수신한 후 증폭(Amplification) 및 필터링(Filtering) 기능을 수행합니다.

- LTI 또는 NLTV 방식으로 동작할 수 있습니다.

- Equalization (등화) 기능을 통해 신호 왜곡을 보정할 수도 있습니다.

(9) Rx CDR/DFE

- CDR (Clock Data Recovery):

- 송신기의 클럭이 포함되지 않은 비동기 신호에서 클럭을 복원하는 역할을 합니다.

- PLL(Phase-Locked Loop)이나 DLL(Delay-Locked Loop) 기술을 사용하여 데이터 타이밍을 맞추는 과정입니다.

- DFE (Decision Feedback Equalizer):

- 채널에서 발생하는 ISI(Inter-Symbol Interference)를 줄이기 위해 피드백 루프를 적용하여 신호를 복구하는 역할을 합니다.

- 채널 감쇠 및 신호 왜곡을 보정하는 역할을 수행합니다.

(10) Sink (수신기)

- 수신된 데이터를 최종적으로 처리하는 블록입니다.

- 일반적으로 FPGA, SoC, ASIC 등의 회로에서 데이터 처리가 이루어집니다.

2. 주요 개념

- LTI (Linear Time-Invariant) vs NLTV (Non-Linear Time-Variant)

- LTI: 선형적인 시간 불변 시스템으로, 고속 신호 처리에서 이상적인 경우를 가정

- NLTV: 실제 환경에서는 온도, 전압, 공정(Process Variation) 등의 영향을 받으며, 비선형적인 요소가 발생할 수 있음

- Total Channel vs Differential Channel

- Total Channel: 전체 신호 경로(송신기~수신기)를 포함하는 모델

- Differential Channel: 차동 신호(Differential Pair) 전송을 위한 채널

- System LTI Impulse Response

- Tx와 Rx Front-End가 LTI 시스템으로 동작할 때, 전체 시스템의 충격 응답(Impulse Response)을 의미함.

- 시스템의 주파수 응답 특성을 결정하는 중요한 요소.

3. 신호 무결성(Signal Integrity) 고려 사항

(1) 클럭 복원 (Clock Data Recovery, CDR)

- 고속 SerDes에서는 별도의 클럭이 전송되지 않으며, CDR을 통해 신호에서 클럭을 복원해야 함.

- PLL 기반 CDR이 많이 사용됨.

(2) ISI (Inter-Symbol Interference)

- 연속된 신호가 이전 신호의 영향을 받아 왜곡되는 현상.

- DFE(Decision Feedback Equalization) 를 활용하여 보정.

(3) Equalization (등화)

- 채널에서 발생하는 감쇠와 지터를 보상하기 위해 Tx Pre-emphasis, Rx Equalization, DFE 기법을 적용.

(4) 신호 감쇠 및 반사

- PCB 레이아웃, 패키지, 커넥터 등에 의한 감쇠와 반사를 최소화해야 함.

- Differential Signaling(차동 신호) 사용이 일반적.

4. 결론

위의 그림은 고속 SerDes 링크의 신호 흐름을 개략적으로 설명한 것으로, 주요 요소는 다음과 같습니다.

- Tx -> 패키지 -> 채널 -> Rx 패키지 -> Rx -> CDR/DFE -> Sink의 흐름으로 신호가 전송됨.

- 신호 무결성(Signal Integrity)을 유지하기 위해 Equalization, CDR, DFE, IBIS 모델 등의 기술이 적용됨.

- 차동 신호(Differential Signaling) 와 LTI/NLTV 시스템 분석이 중요한 요소로 작용.

고속 SerDes 시스템을 설계할 때 위의 요소들을 고려하여 최적화해야 합니다.

'System-on-Chip Design' 카테고리의 다른 글

| 시스템 반도체 설계를 위한 SysML 기반의 기능 분석 (2) | 2025.02.22 |

|---|---|

| SERDES(Serializer/Deserializer)의 개념, 아키텍처, 그리고 응용 분야 (2) | 2025.02.20 |

| Power System for Server (1) | 2025.02.19 |

| Digital Interface for Server system (1) | 2025.02.19 |

| 클라우드 서버 AI 시스템 (0) | 2025.02.19 |