1. 개요 (Abstract)

이 논문은 직렬 데이터 버스(serial data bus)를 통해 데이터를 전송하는 기본적인 방법을 설명하며, SERDES가 이러한 데이터 변환에서 핵심적인 역할을 한다는 점을 강조합니다. SERDES의 기능과 다양한 구현 기법에 대해 설명하는 것이 이 논문의 주요 목적입니다.

2. 서론 (Introduction)

2.1 기존 병렬 데이터 전송 방식의 문제점

과거에는 데이터를 칩 간에 전송할 때, 칩의 입출력 핀(I/O pins) 을 통해 직접 연결하는 방식이 사용되었습니다. 그러나 데이터가 여러 개의 비트(bit)로 이루어져 있기 때문에 병렬 데이터 전송 방식에는 다음과 같은 두 가지 문제가 있습니다.

- 입출력 핀 수 증가 문제

- n비트 데이터를 전송하려면 n개의 입출력 핀이 필요합니다.

- 칩의 크기가 커지고 패키징 비용이 증가합니다.

- 타이밍 문제

- 병렬 데이터의 각 비트가 동시에 전송되어야 하지만, 신호 간 지연(Skew)으로 인해 동기화 문제가 발생할 수 있습니다.

- 고속 동작에서는 타이밍 마진을 맞추기가 어렵습니다.

이러한 문제를 해결하기 위해 병렬 데이터를 직렬 데이터로 변환하여 전송하는 방식(Serial Communication) 이 등장했습니다.

3. SERDES란?

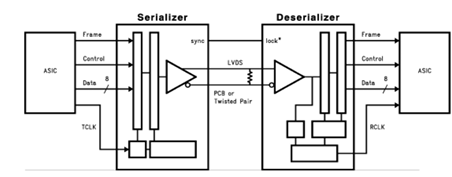

SERDES (Serializer/Deserializer) 는 병렬 데이터를 직렬 데이터로 변환하여 전송한 후, 다시 병렬 데이터로 복원하는 장치입니다. 이를 통해 칩 간 직렬 인터커넥트(serial interconnect) 를 가능하게 하고, 입출력 핀 수와 타이밍 문제를 해결할 수 있습니다.

SERDES는 현대 통신 시스템의 핵심 구성 요소이며, 적절한 SERDES를 선택하는 것은 시스템의 비용(cost) 및 성능(performance) 에 큰 영향을 미칩니다.

II. 고속 SERDES의 아키텍처

고속 Serializer/Deserializer (HSS) 장치는 2.5 Gbps 이상의 속도로 작동하는 입출력(I/O) 인터페이스의 주요 구현 방식입니다. 이러한 장치는 소스 동기 인터페이스(Source Synchronous Interface) 와 차별화되며, 수신기(Receiver)에는 클럭 데이터 복구(Clock Data Recovery, CDR) 회로가 포함되어 있어 신호의 전환 에지를 기반으로 최적의 샘플링 지점을 동적으로 결정합니다. 즉, 별도의 클럭 신호 없이 데이터에서 직접 클럭 정보를 추출합니다.

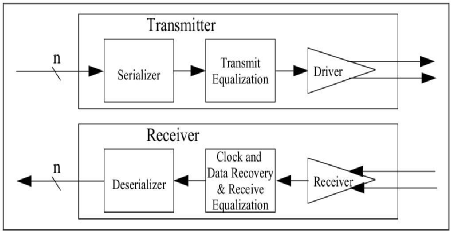

Fig.2는 HSS 장치의 송신 및 수신 채널의 기본 블록 다이어그램을 보여줍니다.

- 송신기(Transmitter) 는 병렬 데이터를 직렬 데이터로 변환(Serialization) 하고, 신호를 보정(Equalization)한 후 차동 신호(differential signal) 로 변환하여 두 개의 인터커넥트 와이어로 전송합니다.

- 수신기(Receiver) 는 차동 신호를 수신하여, CDR 회로를 통해 신호를 보정 및 복구한 후 병렬 데이터로 변환(Deserialization) 합니다.

Fig.2 HSS basic block diagram

송신 또는 수신 채널만 포함된 Serdes 코어를 심플렉스 코어라고 합니다. 채널을 포함하는 Serdes 코어를 단면 코어라고 하며, 전송 및 수신 채널을 모두 포함하는 송신 및 수신 채널이 모두 포함된 Serdes 코어를 전이중 코어라고 합니다. "전이중"이라는 용어가 전기 인터페이스가 전기 인터페이스가 양방향이라는 의미는 아닙니다. 주어진 전기 상호 연결 채널에는 데이터 전송 방향이 고정되어 있습니다. 프로토콜 애플리케이션에 "전이중" 통신이 필요한 경우, 독립적인 송신 및 수신 채널이 필요한 경우 독립적인 상호 연결을 사용하여 인터페이스를 구현합니다.

SerDes에서:

- Simplex SerDes: 단방향 전송 전용 (Tx 전용 또는 Rx 전용).

- Half-Duplex SerDes: 한 번에 한 방향으로만 데이터 전송 가능.

- Full-Duplex SerDes: 독립적인 송신(Tx) 및 수신(Rx) 채널을 사용하여 양방향 통신 가능.

A. Serializer/Deserializer 블록 구조

- Serializer(직렬 변환기)

- n비트 병렬 데이터를 입력받고, 이를 Baud Rate/n 속도로 래치(latch)합니다.

- SerDes 내부의 고속 클럭(high-speed clock) 을 분주하여 병렬 데이터 샘플링 클럭(sample clock) 을 생성합니다.

- 이 클럭은 송신 채널로 데이터를 보내는 로직이 사용할 수 있도록 출력 클럭으로 제공됩니다.

- Deserializer(병렬 변환기)

- 직렬 데이터를 병렬 데이터로 변환하는 역(逆) 기능을 수행합니다.

- SerDes 내부의 고속 클럭을 분주하여 샘플링 클럭을 생성하고, 이 클럭을 출력 클럭으로 제공하여 병렬 데이터를 래칭(latch)하는 로직에서 사용할 수 있도록 합니다.

- 실제 구현에서는 부분적인 병렬 변환을 선행 단계에서 수행할 수도 있습니다.

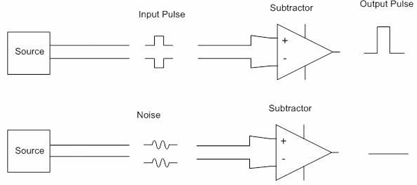

B. 이퀄라이저(Equalizer)

신호 무결성(signal integrity) 문제로 인해 송신기(Tx) 및 수신기(Rx) 에 이퀄라이저(Equalizer) 를 적용하여 채널의 영향을 보정해야 합니다.

- 송신기에서 이퀄라이저를 적용하면, 채널의 주파수 응답 특성의 역전달 함수(Inverse Transfer Function) 를 적용하여 신호를 왜곡(distortion)합니다.

- 이 과정에서 송신기 출력에서는 신호가 왜곡된 것처럼 보일 수 있지만, 수신기 입력에서는 깨끗한 신호가 복원될 수 있도록 조정됩니다.

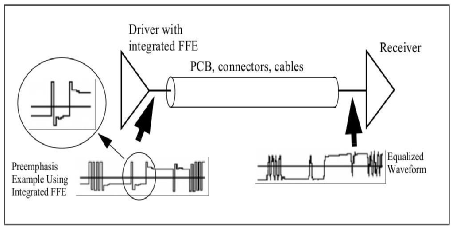

- Fig.4는 송신기에 이퀄라이저를 추가하는 방식의 개념을 보여줍니다.

이 그림은 고속 SerDes(Serializer/Deserializer) 시스템에서 신호 전송 및 이퀄라이제이션(Equalization) 과정을 설명하는 다이어그램입니다.

1. 주요 구성 요소

- Driver with integrated FFE (송신기 + FFE 적용)

- FFE (Feed-Forward Equalization) 를 포함한 송신기입니다.

- FFE는 Pre-emphasis (사전 강조) 를 수행하여 신호를 조정합니다.

- 이를 통해 높은 주파수 성분이 감쇠되지 않도록 보정하여 수신 시 신호 품질을 개선합니다.

- PCB, Connectors, Cables (전송 매체)

- 신호가 인쇄회로기판(PCB), 커넥터, 케이블을 통해 이동합니다.

- 이 과정에서 신호 감쇠(Attenuation) 및 ISI(Inter-Symbol Interference)와 같은 문제들이 발생할 수 있습니다.

- Receiver (수신기)

- 수신기는 전송된 신호를 받아서 복구합니다.

- 수신단에서는 추가적으로 Equalizer(이퀄라이저) 를 적용하여 신호를 보정합니다.

- 보정된 신호(Equalized Waveform)는 더 깨끗한 형태로 출력됩니다.

2. Pre-emphasis (사전 강조) & Equalization (이퀄라이제이션)

- Pre-emphasis (송신 측 FFE 적용)

- 전송선로에서 높은 주파수 성분이 약해지는 문제를 해결하기 위해, 송신기에서 특정한 방식으로 신호를 강조(Pre-emphasis)합니다.

- 그림 왼쪽의 확대된 부분은 Pre-emphasis가 적용된 신호를 보여줍니다.

- 송신 신호가 의도적으로 왜곡된 것처럼 보이지만, 전송 과정에서 감쇠 후 수신기에서 보정되면 정상적인 신호로 복원됩니다.

- Equalization (수신 측 보정)

- 수신기에서는 이퀄라이제이션(Equalization) 회로를 통해 신호를 복구합니다.

- 그림 오른쪽 하단의 신호가 보정된 Equalized Waveform 을 보여주며, 원래의 신호에 가깝게 복구된 것을 볼 수 있습니다.

3. 요약

- SerDes 시스템에서는 높은 속도의 신호 전송 시 신호 감쇠 및 지터(jitter) 문제가 발생할 수 있습니다.

- 송신 측에서는 Pre-emphasis(사전 강조) 기법을 적용하여 신호 왜곡을 조정합니다.

- 수신 측에서는 Equalization(이퀄라이제이션) 기법을 사용하여 신호 품질을 개선합니다.

- 이러한 기술을 적용하면 고속 데이터 전송에서도 신뢰성 높은 신호 복원이 가능합니다.

C. 클럭 및 데이터 복구 (Clock and Data Recovery, CDR)

CDR 회로는 데이터 신호의 전환(transition)을 모니터링하고, 비트 에지(edge) 중간 지점에서 최적의 샘플링 지점을 결정합니다.

- 데이터 전환 타이밍에는 지터(jitter) 가 포함될 수 있기 때문에, CDR은 평균화(averaging) 작업을 수행하여 샘플링 지점이 안정적으로 유지되도록 합니다.

- 심볼 간 간섭(ISI, Inter Symbol Interference) 및 기타 결정적 지터(Deterministic Jitter, DJ) 는 데이터 신호의 주파수 스펙트럼 특성에 따라 달라집니다.

- 데이터의 주파수 스펙트럼이 수백 비트 동안 변화하면, CDR은 최적 샘플링 지점을 동적으로 조정합니다.

D. 차동 드라이버 (Differential Driver)

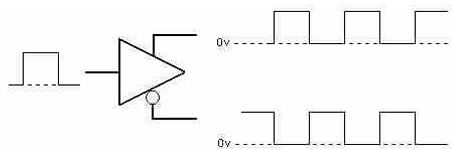

차동 드라이버(Differential Driver) 는 아날로그 회로로 구성되며, 차동 신호(differential signal)의 실제(True) 및 보완(Complement) 신호를 구동하는 역할을 합니다.

- 출력 데이터는 지터(Jitter)를 최소화할 수 있도록 안정적으로 구동되어야 합니다.

E. 차동 수신기 (Differential Receiver)

차동 수신기(Differential Receiver) 는 아날로그 비교기(Comparator) 회로를 기반으로 동작하며, 차동 신호의 실제(True) 및 보완(Complement) 신호를 비교하여 디지털 "0" 또는 "1"의 논리 레벨로 변환합니다.

결론

- 고속 SerDes는 소스 동기 인터페이스와 달리 클럭 데이터를 직접 복구하는 CDR 회로를 포함하여 동작합니다.

- Serializer와 Deserializer 블록은 각각 직렬화/병렬화 기능을 수행하며, 샘플링 클럭을 함께 제공합니다.

- 이퀄라이저(Equalizer) 는 신호 무결성을 유지하기 위해 송신기 및 수신기에서 사용됩니다.

- CDR 회로는 최적의 데이터 샘플링 지점을 결정하고, 차동 드라이버 및 수신기는 신호 품질을 극대화하는 역할을 합니다.

이러한 구조를 통해 고속 SERDES 는 2.5 Gbps 이상의 데이터 전송을 안정적으로 수행할 수 있습니다.

마무리

이 논문은 SERDES의 기본 개념과 병렬 데이터에서 직렬 데이터로 변환하는 이유를 설명하면서, SERDES의 여러 가지 아키텍처를 다룰 것으로 보입니다. 이후 내용에서는 아마도 각 아키텍처의 특징과 응용 사례를 구체적으로 설명할 것입니다.

III. SerDes의 종류 (Types of SerDes)

SerDes(Serializer/Deserializer)는 데이터 전송 방식에 따라 여러 가지 아키텍처가 존재하며, 각각의 방식은 특정한 응용 분야에 적합하도록 설계되었습니다. 이 절에서는 대표적인 4가지 유형의 SerDes 에 대해 설명합니다.

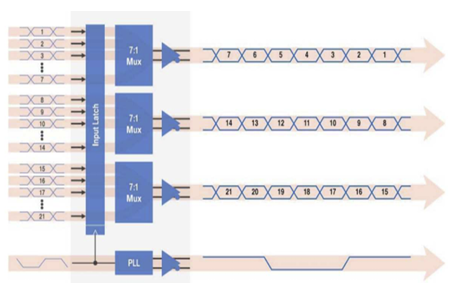

A. 병렬 클럭 SerDes (Parallel Clock SerDes)

이 방식은 주로 PCI, UTOPIA, 프로세서 버스, 제어 버스 등과 같은 넓은 병렬 데이터 버스를 직렬화할 때 사용됩니다.

특징

- 하나의 멀티플렉서를 사용하여 전체 버스를 직렬화하는 것이 아니라, n:1 멀티플렉서 여러 개를 사용하여 각각의 데이터 섹션을 개별적으로 직렬화함.

- 직렬화된 데이터 스트림은 추가적인 클럭 신호와 함께 수신기로 전송됨.

- 데이터와 클럭 신호가 여러 개의 신호 쌍(pairs)을 통해 전송되므로, 신호 쌍 간의 스큐(skew)를 최소화해야 함.

- 저비용(Price/Performance) 이 뛰어나며, 긴 거리(수 미터 이상) 전송에도 적합함.

응용 분야

- 넓은 병렬 버스를 직렬화하여 여러 미터의 케이블을 통해 전송해야 하는 경우

- 병렬 버스 폭이 21비트, 28비트, 48비트인 경우

(예: PCI Express, 프로세서 메모리 인터페이스)

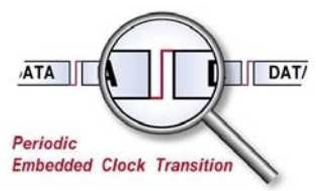

B. 내장 클럭 SerDes (Embedded Clock SerDes)

이 방식에서는 데이터 버스와 클럭을 하나의 직렬 신호 쌍에 포함(embedded) 시켜 전송합니다.

특징

- 매 전송 주기마다 2개의 클럭 비트(0과 1)를 데이터 스트림에 삽입

→ 이를 통해 직렬 스트림 내에서 각 데이터 워드의 시작과 끝을 구분할 수 있음.

(이러한 이유로 "Start-Stop Bit SerDes"라고도 불림) - 데이터 페이로드 크기가 바이트(8비트) 단위로 고정되지 않음.

→ 예: 10비트, 18비트 등 다양한 크기의 데이터 전송 가능. - 수신기(Receiver)는 주기적인 임베디드 클럭의 상승 에지(Rising Edge)를 찾아 자동으로 동기화(lock) 가능.

- 추가적인 시스템 개입 없이 수신기가 "Lock to Random Data(무작위 데이터 동기화)" 기능을 수행

→ 수신기가 원격 모듈(remote module)에 위치한 경우 유용 - 송신기와 수신기의 외부 기준 클럭(reference clock)에 대한 지터(jitter) 요구 사항이 완화됨.

응용 분야

- 비바이트(byte) 기반이 아닌 원시 데이터(raw data) + 추가 신호(제어, 패리티, 프레임, 동기화, 상태 정보 등)를 전송하는 시스템

- 기지국(Base Stations), 자동차 영상/비디오, 센서 시스템

- 예: A/D 컨버터(ADC), 카메라, 디스플레이 모듈 등이 처리 유닛과 데이터를 주고받을 때 사용

C. 8b/10b SerDes

이 방식에서는 8비트 데이터를 10비트 코드로 변환하여 전송하는 IBM이 1980년대 개발한 방식입니다.

특징

- 8비트 데이터를 10비트 코드로 변환 후 직렬화(8b/10b 인코딩)

- 주기적인 에지 전환(edge transition)을 포함하여 수신기가 동기화할 수 있도록 함.

- DC 밸런스(DC Balance) 보장

- "1"과 "0"의 개수를 맞춰서 AC 커플링(AC-coupled loads), 긴 케이블(long cables), 광 모듈(optical modules)과 호환 가능.

- 수신기는 "Comma Character"를 사용하여 10비트 코드 경계를 식별

- Comma Character: 일반 데이터 패턴에서 절대 등장하지 않는 특별한 비트 시퀀스

- 이를 이용하여 수신기가 데이터 정렬(alignment)을 수행함.

- 외부 기준 클럭(reference clock)에 대한 주파수 및 지터 제어가 필요

- 정확한 클럭 주파수와 낮은 지터가 요구됨.

응용 분야

- 바이트 기반(byte-oriented)의 데이터 전송

- 예: 이더넷(Ethernet), 파이버 채널(Fibre Channel), 인피니밴드(InfiniBand)

- 백플레인(Backplane), 케이블 및 광통신(Fiber)에서 셀 또는 패킷 데이터를 전송

- 데이터 전송 속도

- 1.0625 Gbps, 1.25 Gbps, 2.5 Gbps, 3.125 Gbps 등 다양한 속도 지원

- 8b/10b 인코딩은 전자기 방사(EMI)를 줄이는 데 유리함

- 연속적인 "1" 또는 "0" 개수가 최대 5비트로 제한됨

- 예: 1 Gbps 링크에서 최대 주파수는 1 GHz, 최소 주파수는 200 MHz로 제한됨.

- 오류 감지(Error Detection) 및 제어 코드 지원

- 잘못된 10비트 코드 감지 가능 → 오류 감지 기능 수행

- 제어 코드(Control Words) 지원 → 프레임 마커, 오류 플래그, 패킷 정렬 기능 포함

D. 비트 인터리빙 SerDes (Bit Interleaving SerDes)

이 방식은 여러 개의 느린 SONET/SDH 또는 8b/10b 직렬 스트림을 하나의 더 빠른 직렬 스트림으로 다중화(Multiplexing) 하는 방식입니다.

특징

- 여러 개의 저속 직렬 스트림을 하나의 고속 직렬 스트림으로 다중화

- 송신기(Transmitter)에서 다중화된 신호를 비트 단위로 인터리빙(Bit Interleaving)

- 수신기(Receiver)에서는 이를 원래의 개별 스트림으로 복구(Demultiplexing)

- 입력 스트림의 순서(order)가 반드시 보장되지 않음

- 입력 채널 1의 데이터가 반드시 수신기 채널 1에서 출력되지 않을 수도 있음.

- 하지만, 개별 패킷/셀 데이터가 독립적으로 전송되므로 문제가 되지 않음.

응용 분야

- 스위치(Switch) 및 라우터(Router)에서 백플레인을 통한 대역폭 확장

- 여러 개의 8b/10b 직렬 스트림을 다중화하여 하나의 고속 링크로 전송

- 기존 백플레인을 그대로 유지하면서 더 높은 대역폭을 제공할 수 있음.

결론

SerDes 아키텍처는 응용 목적에 따라 적절한 방식을 선택해야 합니다.

SerDes 유형특징주요 사용 사례

| 병렬 클럭 SerDes | 데이터와 클럭을 별도로 전송 | PCI, 프로세서 버스 |

| 내장 클럭 SerDes | 데이터 스트림 내 클럭 포함 | 기지국, 센서 시스템 |

| 8b/10b SerDes | 8비트를 10비트 코드로 변환하여 전송 | 이더넷, 파이버 채널 |

| 비트 인터리빙 SerDes | 여러 개의 저속 스트림을 하나의 고속 스트림으로 다중화 | 스위치, 라우터 |

고속 데이터 전송 시스템을 설계할 때, 데이터 특성과 전송 거리, 지터 및 동기화 요구 사항을 고려하여 적절한 SerDes 방식을 선택해야 합니다.

'System-on-Chip Design' 카테고리의 다른 글

| 동적 클럭 게이팅 (Dynamic Clock Gating) (0) | 2025.03.01 |

|---|---|

| 시스템 반도체 설계를 위한 SysML 기반의 기능 분석 (2) | 2025.02.22 |

| Serdes (Serializer/Deserializer) (0) | 2025.02.20 |

| Power System for Server (1) | 2025.02.19 |

| Digital Interface for Server system (1) | 2025.02.19 |