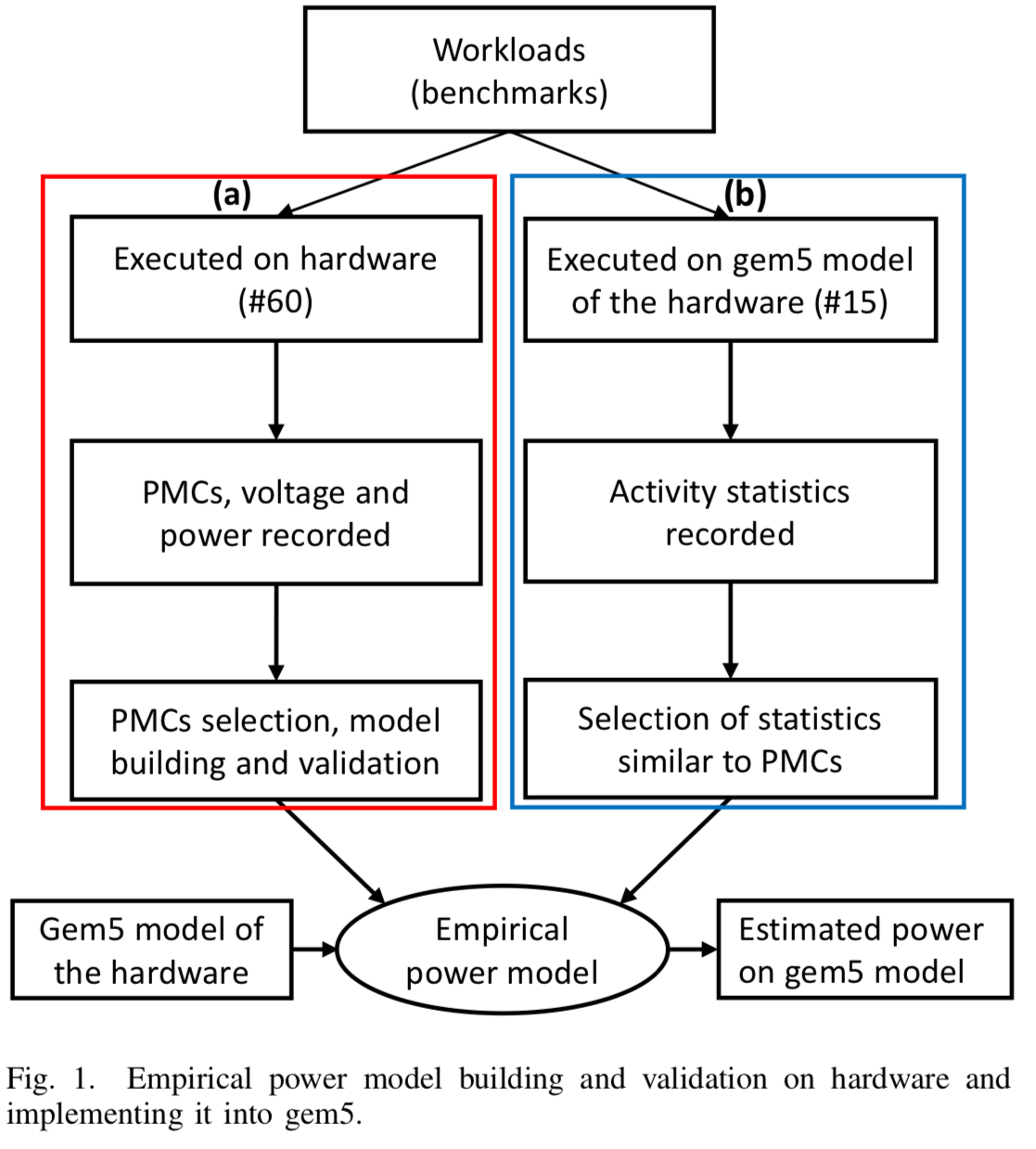

현대 CPU들에 대한 파워 모델링은 파워 관리 접근 방식을 안내하고 다양한 구성(예: 코어 수, 캐시 크기 등)으로 시스템의 설계 초기 단계에서 파워-퍼포먼스 트레이드오프를 조사할 수 있게 해주어 중요합니다. 전체 시스템 아키텍처 시뮬레이터인 gem5와 결합된 파워 시뮬레이터는 이러한 탐색을 가능하게 합니다. 하지만, McPAT과 같은 기존 파워 시뮬레이터의 정확도는 추상화와 명세 오류로 인해 낮게 알려져 있으며, 이는 잘못된 연구 결론으로 이어질 수 있습니다. 이 논문에서, 우리는 측정된 데이터로부터 구축된 정확한 파워 모델을 제시하며, 이 모델은 gem5에 통합되어 시뮬레이션된 쿼드-코어 ARM Cortex-A15의 파워 소비를 추정하기 위해 사용됩니다. Performance Monitoring Counters (PMCs)를 기반으로 하는 파워 모델링 방법론은 gem5에서 통합된 모델을 구축하고 평가하는 데 사용됩니다. 우리는 먼저 이 방법론을 실제 하드웨어에서 9개의 Dynamic Voltage and Frequency Scaling (DVFS) 수준과 4개의 코어 매핑(2,160 샘플)에서 60개의 워크로드로 검증하며, 추정된 파워와 실제 측정된 파워 사이의 평균 오류가 6% 미만임을 보여줍니다. gem5 활동 통계와 하드웨어 PMCs 사이의 상관 관계를 조사하여 쿼드-코어 ARM Cortex-A15을 나타내는 gem5 모델을 구축합니다. 실제 하드웨어와 gem5에서 4개의 DVFS 수준에서 15개의 워크로드로 실험적 검증이 수행되어 gem5 시뮬레이션 활동 통계와 하드웨어 PMCs 사이의 차이가 추정된 파워 소비에 어떻게 영향을 미치는지를 이해하게 됩니다.

1. Introduction & Motivation

현대 시스템에서 파워는 주요 설계 고려 사항이며, 특히 임베디드 및 모바일 장치에서 더욱 그러합니다. 이는 현대 시스템온칩(SoCs)에서의 파워 소비를 추정하고 설계 시점에서 적절한 파워-퍼포먼스 트레이드오프를 식별하기 위한 정확하고 안정적인 모델에 대한 수요를 증가시켰습니다. 그 결과, McPAT [1], CACTI [2], Wattch [3]와 같은 다양한 SoC 파워 추정 도구가 개발되어 여러 파워 관련 연구 아이디어 [4]-[8]를 평가하기 위해 사용되었습니다. 이 도구들은 CPU, 캐시, 메모리의 파워/에너지 소비를 시뮬레이트하는 데 사용됩니다. 일반적으로, 아키텍처 시뮬레이터는 CPU/SoC의 마이크로아키텍처 활동을 설명하는 통계를 얻기 위해 사용되며, 이는 시뮬레이터의 마이크로아키텍처 및 물리적 구현 세부 사항과 함께 파워 시뮬레이터로 전달됩니다.

파워 모델은 크게 두 가지 주요 카테고리로 나뉩니다: 바텀업 파워 모델, 예를 들어 앞서 언급한 McPAT, CACTI, Wattch, 그리고 탑다운 파워 모델, 예를 들어 성능 모니터링 카운터(PMC)-기반 모델 [9]-[12].

바텀업 파워 모델은 CPU 사양(예: 캐시 크기, 파이프라인 수)을 취하고 먼저 CPU 복잡도, 구성 요소 수 및 영역을 추정한 다음 다양한 작업을 수행하는 데 필요한 스위칭 활동량을 추정함으로써 파워를 추정하려고 시도합니다. Wattch는 아키텍처 수준 파워 시뮬레이션을 위한 프레임워크입니다. CACTI는 업계 표준 ITRS 로드맵을 기반으로 한 디바이스 모델을 사용하여 캐시 및 메모리 접근 시간, 사이클 시간, 영역, 누설 및 동적 파워를 추정하기 위한 모델링 도구입니다. McPAT은 통합 파워, 영역 및 타이밍 모델링 프레임워크입니다. 특히 McPAT은 사용 용이성과 준비성 때문에 인기를 얻었으며, 파워 소비를 추정하기 위해 활동 인자들이 있는 단일 구성 파일만 필요합니다 [13]. 설계 공간 탐색(DSE)에 대한 유연성이 제공되는 것에도 불구하고, 이러한 시뮬레이션 도구들은 상당한 오류를 보고하고 있으며 [13]-[15], 종종 그 한계를 완전히 이해하지 못한 채 사용되어 잘못된 연구 결론으로 이어질 수 있습니다 [16].

탑다운 파워 모델은 측정된 경험적 데이터를 사용하여 특정 CPU 구현을 위해 구축됩니다. 이러한 파워 모델은 PMC 데이터와 CPU/SoC에서 측정된 파워 소비로부터 구축됩니다 [17], [18]. 많은 CPU에는 L2 캐시 미스, 추측적으로 실행된 명령과 같은 특정 아키텍처 및 마이크로아키텍처 이벤트를 계산하는 PMC가 있습니다. 이러한 이벤트는 CPU 동작을 결정하는 데 사용될 수 있으므로 CPU 파워 소비를 추정하는 데 사용될 수 있습니다. PMC를 입력으로 사용하는 회귀 기반 모델은 CPU 파워를 추정하는 데 효과적임이 널리 입증되었습니다 [9]-[12]. 하지만, 하드웨어에서 PMC를 수집하는 것은 간단하지 않으며 필요한 하드웨어 플랫폼은 종종 연구자들에게 사용할 수 없습니다. 바텀업(특정 CPU에서만 유효하므로 유연하지 않음)보다 유연성이 떨어지는 탑다운 접근 방식은, 이 작업에서 제시된 것처럼, 그 구현에 대해 정확도가 크게 향상되고 잘 이해됩니다.

아키텍처 시뮬레이션 도구를 사용하는 것은 실제 하드웨어에서 실험을 실행하는 것보다 일반적으로 더 편리하고 유연합니다. 이러한 도구는 CPU/SoC의 성능(예: 벤치마크/워크로드의 실행 시간)을 평가하고 성능 병목을 이해하기 위해 하드웨어 이벤트(예: L1 명령 캐시 접근 수)를 시뮬레이트하는 데 사용됩니다. 또한 다양한 구성(예: 코어 수, 캐시 크기 등)으로 DSE를 수행해 볼 수 있도록 합니다. SimpleScalar [19]는 CPU 성능 분석과 마이크로아키텍처 모델링을 위해 사용되는 도구 세트이며, 다수의 명령 세트 아키텍처(ISAs): Alpha, PISA, ARM, x86을 지원합니다. MARSSx86 [20]은 PTLsim에 기반한 사이클 정확한 전체 시스템 시뮬레이터입니다. 이는 x86 ISA만을 지원합니다. gem5 시뮬레이터 [21]는 여러 ISAs(Alpha, ARM, SPARC, x86)를 지원하는 모듈러하고 유연한 시뮬레이션 플랫폼입니다. 이는 활발한 개발 커뮤니티를 가지고 있으며 많은 기관들로부터 자주 기여를 받고 있으며, 자유롭게 사용할 수 있고 최근 연구에서 널리 사용됩니다. 따라서, 우리는 이 작업을 위해 gem5를 고려하고 섹션 II.C에서 보다 자세히 논의합니다. 바텀업 접근법(예: McPAT)은 gem5와 함께 사용되어 파워 소비를 추정합니다. 그러나, 많은 연구에서 이미 실제 하드웨어에서 측정된 파워와 추정된 파워 사이에 상당한 오류를 보고했습니다. 최근 Butko 등 [22]은 이 작업에서 사용된 동일한 장치(ODROID-XU3 보드)를 시뮬레이트하기 위해 gem5와 McPAT를 사용했습니다. 그들은 측정된 에너지와 모델링된 에너지 사이에 평균 24%의 오차를 발견했습니다.

저자의 최선의 지식으로는, 정확한 탑다운 접근법이 gem5와 같은 유연한 아키텍처 시뮬레이터에 이전에 통합된 적이 없습니다. 이 작업에서, 우리는 하드웨어에서 검증된 탑다운 PMC 기반 파워 모델을 구축하고 gem5 시뮬레이션 프레임워크에 통합했습니다. 여기서, 우리는 x86 기반 프로세서가 아닌 모바일 애플리케이션에 에너지 효율이 중요한 고성능 쿼드코어 ARM Cortex-A15를 고려합니다. 우리는 최근 개발된 경험적 PMC 기반 파워 모델링 방법론 [17], [23]을 사용하여 하드웨어 PMC 이벤트(활동 통계)가 gem5에서 직접 동등하게 쉽게 사용할 수 있는 통합 모델을 생성하고 평가했습니다. 우리는 먼저 실제 하드웨어에서 다양한 동적 전압 및 주파수 스케일링(DVFS) 수준과 코어 매핑에서 측정된 파워 읽기를 가진 다양한 워크로드로 이 방법론을 검증했습니다. 그런 다음 하드웨어 플랫폼과 유사한 gem5 모델이 생성되어 gem5에서 수집된 활동 통계를 입력으로 사용하는 통합 파워 모델을 평가하는 데 사용되었습니다.

이 논문의 주요 기여는 다음과 같습니다:

• gem5 활동 통계와 하드웨어 PMC 사이의 상관 관계 조사 및 Odroid-XU3에서 쿼드코어 ARM Cortex-A15 클러스터를 닮은 gem5 모델 구축;

• 이 모델을 gem5에 구현하고 정확도를 평가함.

우리는 경험적 PMC 기반 파워 모델링, 실험 설정, 하드웨어에서 구축된 경험적 파워 모델을 포함한 제안된 방법론을 섹션 II에서 제시합니다. 또한 gem5에서 쿼드코어 ARM Cortex-A15의 모델링, gem5 파워 모델과 실제 하드웨어 사이의 차이 평가, 그리고 파워 모델을 gem5에 구현하는 것을 설명합니다. 섹션 III은 실험 결과를 설명하고, 마지막으로 섹션 IV에서 논문을 결론집니다.

2. Emperical Power Model

gem5에 경험적 파워 모델을 구현하기 위해, 우리는 먼저 모든 사용 가능한 DVFS 수준에서 하드웨어 플랫폼에서 60개의 워크로드를 실행하면서 PMC, 전압 및 파워를 캡처했으며, 이는 그림 1(a)에서 보여줍니다. 하드웨어 플랫폼과 워크로드는 섹션 II.A에서 더 자세히 논의됩니다. 그 다음, 우리는 파워 추정을 위한 최적의 PMC 이벤트를 선택하고 정확하고 안정적인 파워 모델을 생성하기 위해 모델 구축 방법론 [17]을 사용했으며, 이는 섹션 II.B에서 더 자세히 설명됩니다. 이어서, 우리는 하드웨어 플랫폼과 유사한 아키텍처 모델을 gem5 시뮬레이션에 생성하고 그 위에서 15개의 워크로드(60개 중 일부)를 실행하면서 결과 활동 통계를 기록했습니다, 그림 1(b)에서 보이듯이. 우리는 활동 통계를 분석하고 선택된 하드웨어 PMC 이벤트에 해당하는 것들을 식별하여 gem5 요구 사항(섹션 II.C)을 고려하여 경험적 파워 모델을 구축했습니다. 그 다음, 우리는 섹션 II.D에서 자세히 설명한 대로 선택된 활동 통계를 사용하여 경험적 파워 모델을 gem5 시뮬레이터에 구현했습니다. 마지막으로, 우리는 섹션 III에서 실제 하드웨어에서 gem5 요구 사항(즉시 사용 가능한 활동 통계)을 고려하여 구축된 경험적 파워 모델을 평가했습니다. gem5 시뮬레이터에서 파워 모델을 직접 테스트하고 시연하기 위해, 우리는 동일한 15개의 워크로드를 하드웨어 플랫폼에서 실행하고 PMC 이벤트를 기록했습니다. 더 나아가, 우리는 이 데이터를 gem5의 데이터와 비교하고 두 데이터 세트 모두를 동일한 파워 모델에 공급하여 두 가지 사이의 추정된 파워에서의 편차를 정량화했습니다.

'IT' 카테고리의 다른 글

| 라즈베리파이 윈도우11 설치 (2) (2) | 2024.03.28 |

|---|---|

| 라즈베리파이 윈도우11 설치 (1) (0) | 2024.03.28 |

| Life360의 회사 소개 (1) | 2024.03.19 |

| Global City List (1) | 2024.03.18 |

| 링크 코드의 해석 (0) | 2023.12.17 |