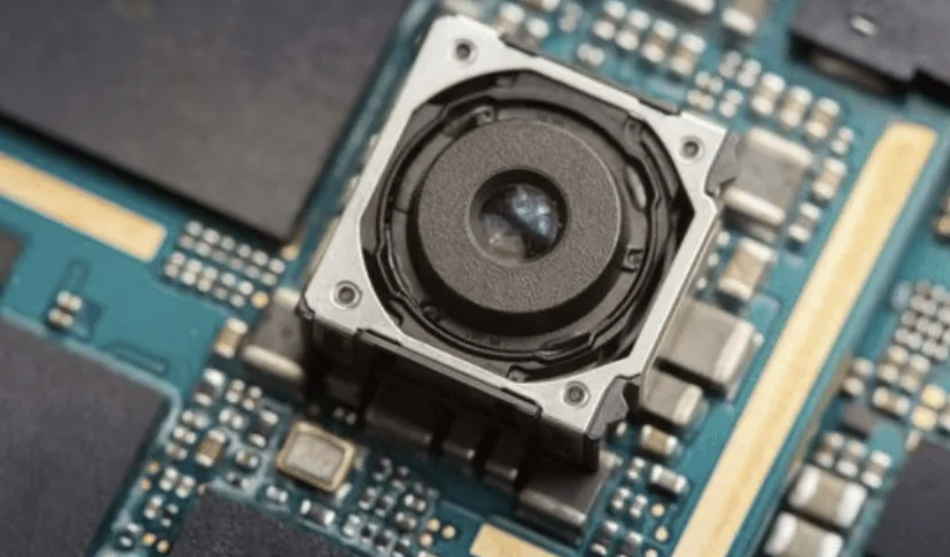

이미지 센서를 활용한 전자 시스템 설계는 광학적 특성과 전기적 신호 처리 간의 복잡한 상호작용을 요구합니다. 고해상도 및 고속 데이터 전송이 필수적인 현대 응용 분야에서는 회로도 설계 단계부터 PCB 레이아웃에 이르기까지 신호 무결성(SI)과 전원 무결성(PI)을 종합적으로 고려해야 합니다. 본 보고서는 이미지 센서 기반 시스템의 설계 제약 조건을 물리적 특성, 전기적 요구 사항, 제조 공정의 관점에서 분석하며, SI/PI 최적화를 위한 핵심 전략을 체계적으로 제시합니다.

1. 이미지 센서의 물리적 특성과 PCB 통합 과제

1.1 광전 변환 메커니즘과 양자 효율

CMOS 이미지 센서의 핵심인 포토다이오드는 실리콘 기반 pn 접합을 통해 광자를 전하로 변환합니다. 파장 450nm 청색광의 경우 1μm 두께 실리콘 층에서 90% 흡수되는 반면, 650nm 적색광은 동일 두께에서 20%만 흡수됩니다. 이 차이는 픽셀 구조 설계 시 빛의 투과 깊이와 포텐셜 기울기 형성 방식을 고려해야 함을 시사합니다. 양자 효율(QE)은 식

로 표현되며, 실제 설계에서는 수광부 상부 막질의 반사 손실과 FF(Fill Factor)를 최소화하는 레이아웃이 필수적입니다.

1.2 열적 영향과 신호 대잡음비(SNR)

이미지 센서의 암전류(dark current)는 온도가 8°C 상승할 때마다 약 2배 증가하는 특성을 보입니다. 삼성전기의 Cavity PCB 기술은 이미지 센서 실장부 두께를 0.15mm까지 축소하면서도 금속 기반 열확산 구조를 적용해 열저항을 15% 감소시켰습니다. 특히 자동차 카메라 모듈의 경우 패시브 쿨링 환경에서 동작하므로, PCB 기판 자체를 열싱크로 활용하는 설계 기법이 중요합니다.

2. 회로도 설계 단계의 전기적 제약 조건

2.1 전원 아키텍처 최적화

고해상도 센서의 경우 아날로그(VAA), 디지털(VDD), 입출력(VDDIO) 전원 레일을 분리하여 설계해야 합니다. ON Semiconductor는 VAA 전원에 LDO를, 고전류 구간에는 스위칭 레귤레이터를 권장하며, 원격 전압 센싱(remote sensing)을 통해 PCB 트레이스의 IR Drop 영향을 보상하는 기법을 제시합니다. 16MP 센서의 경우 피크 전류가 500mA에 달하므로, 전원 평면 임피던스는 50mΩ 이하로 유지해야 합니다.

2.2 아날로그-디지털 변환기(ADC) 통합

Omnivision OV02686-H38A 모듈은 10비트 ADC를 내장하여 PCB 외부 회로를 간소화했으나, 고속 인터페이스 설계 시 클록 지터를 50ps 미만으로 제어해야 합니다. MIPI D-PHY 표준의 경우 1.2Gbps 전송률 달성을 위해 100Ω 차동 임피던스 정합이 필수적이며, 인트라 페어 길이 편차는 150μm 이내로 관리해야 합니다.

3. 고속 신호 무결성을 위한 PCB 레이아웃 기법

3.1 임피던스 제어 전략

MIPI 인터페이스의 경우 미세 스트립라인 구조에서 유전체 두께(h) 대비 트레이스 폭(w) 비율이 h/w=0.8일 때 50Ω 단일 종단 임피던스를 달성합니다. 삼성전기는 25μm 두께 FR-4 기판에서 75μm 트레이스 간격을 유지해 커플링 계수를 3% 이하로 억제하는 시뮬레이션 기법을 개발했습니다. 고주파 손실을 줄이기 위해 역방향 형상 MLCC 커패시터를 적용하면 ESL을 기존 대비 4배 감소시킬 수 있습니다.

3.2 크로스토크 완화 기법

3D 웨이브 시뮬레이션 결과, 5h 간격(유전체 두격 h=25μm 시 125μm)으로 트레이스를 배치할 경우 인접 신호 간 누화를 -40dB 미만으로 제한할 수 있습니다. Altium Designer의 3D 전자기장 해석 도구는 10GHz 대역에서 S-파라미터를 예측하여 공진 현상을 사전에 탐지합니다. 특히 플렉시블 PCB 구간에서는 구리 트레이스의 피로 수명을 높이기 위해 롤드 애닐링(RA) 구리 재질을 단층 구조로 적용하는 것이 효과적입니다.

4. 전원 무결성 관리 및 열 설계

4.1 디커플링 커패시터 네트워크

센서 전원 핀 근처에 0.1μF MLCC를 100MHz 이상 고주파 대역에, 10μF 탄탈럼 커패시터를 1MHz 이하 저주파 대역에 배치하는 이중 대역 필터링 기법이 효과적입니다. ON Semiconductor는 전원 레일별로 3:1 커패시터 비율(예: VAA 3개, VDD 1개)을 권장하며, 커패시터 패드의 비아 배열을 옵션 B(그림 12) 방식으로 설계해 ESL을 30pH까지 낮출 수 있습니다.

4.2 열확산 구조 설계

자동차 카메라 모듈의 열저항 모델 Tj=Ta+θja(Ptotal) 에서, 금속 코어 PCB를 적용할 경우 θ_{ja}를 15°C/W에서 8°C/W로 개선할 수 있습니다. 삼성전기의 Cavity PCB 기술은 이미지 센서 하부에 구리 필을 형성하여 열전도율을 380W/mK 수준으로 향상시켰습니다. 고전류 구간의 전원 평면에는 0.5mm 직경의 열비아를 1mm 간격으로 배열하는 것이 효과적입니다.

5. 패키징 기술과 제조 공정의 상호작용

5.1 COB vs CSP 패키징

Chip on Board(COB) 방식은 와이어 본딩 공정에서 25μm 금선을 사용할 경우 1.5nH/mm의 인덕턴스를 발생시키는데 반해, Chip Scale Package(CSP)는 솔더 범프를 이용해 패키지 전체 인덕턴스를 0.5nH 미만으로 낮출 수 있습니다. 그러나 CSP의 경우 BGA 패드 피치가 0.4mm 이하로 축소되므로, PCB의 유전체 두께를 50μm 미만으로 제어해야 임피던스 불연속을 방지할 수 있습니다.

5.2 HDI 제조 공정 한계

10층 이상의 HDI 보드에서 레이저 비아 직경은 75μm, 패드 직경은 150μm가 최소 제조 한계이며, 임피던스 편차를 5% 이내로 유지하려면 트레이스 폭 편차를 ±2μm 미만으로 관리해야 합니다. 플렉시블 PCB의 경우 폴리이미드 기판 두께 25μm 시 최소 굽힘 반경은 1.5mm로 제한되며, RA 구리 도금을 적용하면 100,000회 굽힘 주기 후에도 트레이스 저항이 10% 이내로 유지됩니다.

6. 다중 보드 시스템과 EMC 대응 전략

6.1 인터보드 커넥터 선정

Samtec QTE 시리즈 40핀 커넥터는 56Gbps NRZ 신호 전송 시 -15dB 삽입 손실을 보장하며, 지그재그 핀 배열을 통해 근단 크로스토크를 2% 미만으로 억제합니다. 고주파 특성 개선을 위해 보드 간 접지 연결은 1mm 간격으로 최소 4개 이상 배치해야 하며, 차동 페어 당 1개의 접지 핀을 할당하는 것이 효과적입니다.

6.2 EMI 차폐 기법

차동 트레이스 상부에 50μm 두께 철-니켈 합금 차폐막을 적용할 경우 1GHz 대역에서 30dB 이상의 차폐 효과를 달성할 수 있습니다. 특히 플렉시블 케이블 구간에서는 구리 폴리이미드 기반의 지오메트릭 차폐 구조가 유연성과 EMI 성능을 동시에 만족시킵니다.

결론: 종합적 설계 접근법의 필요성

이미지 센서 기반 시스템의 성능은 광학적 특성, 반도체 공정, PCB 설계의 삼각 균형에 의해 결정됩니다. 3D 워페지 시뮬레이션을 통한 열-기계적 결합 해석, 다중 물리장 기반의 SI/PI 통합 최적화, 그리고 HDI 제조 공정의 미세 공차 관리가 미래 설계 과제로 대두되고 있습니다. 특히 자율주행 차량용 카메라 모듈의 경우 ASIL-D 기능안전 등급 달성을 위해 신호 체인 전 구간의 FMEA 분석이 필수적이며, 이는 회로도 단계부터 PCB 레이아웃, 패키징에 이르는 전 과정에 걸친 시스템 수준의 검증 프로세스를 요구합니다. 신뢰성 있는 이미지 센서 시스템 구현을 위해서는 물리적 현상에 대한 심층적 이해와 제조 공정의 한계를 동시에 고려한 종합적 설계 철학이 필요합니다.

'IT' 카테고리의 다른 글

| PCB Design Rule, Trace와 Spacing (4) | 2025.03.15 |

|---|---|

| CMOS, BSI CMOS, Stacked CMOS, and Global Shutter (0) | 2025.03.12 |

| SEC EDGAR에서 최신 10-K 보고서 URL 가져오기 (1) | 2025.03.09 |

| UART (Universal Asynchronous Receiver Transmitter) 회로의 이 (0) | 2025.03.02 |

| SPI (Serial Peripheral Interface) 회로 (0) | 2025.03.02 |