저전력 설계를 위해 표준 셀 라이브러리를 이해해야 합니다. 표준 셀의 셀 높이, 임계 전압(VT) 종류, 전력 게이팅 셀, 아이솔레이션 셀, 레벨 시프터, 메모리 인터페이스 설계 등은 전력 최적화와 성능 균형에 직접적인 영향을 미치기 때문입니다. 이를 통해 전력 소모를 최소화하고 성능 요구사항을 충족하는 효율적인 SoC 전력 아키텍처를 설계할 수 있습니다.

12.1 표준 셀 라이브러리

12.1.1 셀 높이와 성능

표준 셀 라이브러리는 성능, 전력 및 면적 요구사항에 맞게 튜닝됩니다. 셀 높이는 트랙 단위로 측정되며 타이밍과 라우팅 특성에 크게 영향을 미칩니다.

- Tall Track Height Libraries (11-12 tracks): 복잡한 라우팅과 더 큰 구동력 트랜지스터를 지원하지만 누설 전력이 높습니다.

- Low Track Height Libraries (7-8 tracks): 면적 효율성이 뛰어나지만 구동력이 낮아 고속 설계에는 부적합합니다.

- Standard Track Height Libraries (9-10 tracks): 면적 효율성과 성능의 균형을 제공하며 일반적으로 많이 사용됩니다.

12.1.2 임계 전압 변형(Threshold Voltage Variants)

전력 및 성능을 최적화하기 위해 서로 다른 임계 전압을 사용하는 라이브러리를 선택할 수 있습니다:

- High-VT Libraries: 낮은 누설 전력과 성능 감소; 비타이밍 크리티컬 경로에 적합합니다.

- Low-VT Libraries: 고속 성능을 제공하지만 누설 전력이 크며 성능이 중요한 경로에 사용됩니다.

- Regular-VT Libraries: 성능과 누설 전력의 균형을 제공합니다.

추가 기법:

- 긴 채널 길이의 게이트를 사용하여 누설 전력 감소.

- 직렬 트랜지스터의 "stack-effect"를 활용하여 누설 전력 최소화.

12.1.3 표준 셀 라이브러리 모델링

표준 셀 라이브러리는 트랜지스터 레벨의 세부 정보를 숨기고 설계자가 쉽게 사용할 수 있도록 추상 모델을 제공합니다. 주요 모델 유형은 다음과 같습니다:

- Timing Models: 다중 코너 합성 및 타이밍 분석 지원.

- Physical Models: 전력 및 신호 포트를 포함하는 레이아웃 추상 제공.

- Functional Models: 게이트 레벨 넷리스트 시뮬레이션 지원.

- Power Models: 동적 및 누설 전력 최적화를 지원.

- Test Models: ATPG(Automatic Test Pattern Generation) 및 결함 커버리지 검증 지원.

12.1.4 표준 셀 라이브러리 특성화

최신 반도체 기술은 온도 반전과 전압 스케일링과 같은 복잡성을 포함합니다:

- Temperature Inversion (온도 반전): 90nm 이하 공정에서는 VDD 감소로 인해 온도가 증가할수록 게이트 지연이 감소하는 현상이 발생합니다.

- New Library Timing Models (새로운 라이브러리 타이밍 모델): CCS(Composite Current Source) 모델이 다중 전압 및 온도 반전을 정확히 예측하기 위해 사용됩니다.

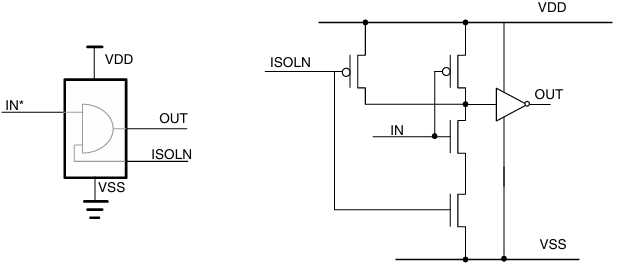

12.2 특수 셀 - 아이솔레이션 셀(Isolation Cells)

아이솔레이션 셀은 전력 도메인이 전원이 꺼질 때 플로팅 입력 및 크로우바 전류를 방지합니다.

12.2.1 신호 아이솔레이션 기법

세 가지 주요 아이솔레이션 방식이 있습니다:

- Clamp to Logic '0': AND 게이트 스타일 아이솔레이션 셀 사용.

- Clamp to Logic '1': OR 게이트 스타일 아이솔레이션 셀 사용.

- State Retention Isolation (상태 유지 아이솔레이션): 출력의 마지막 상태를 유지하기 위해 래치를 사용.

설계 지침:

- 글로벌 항상 켜짐(always-on) 신호를 사용하여 제어.

- 동시 절전 및 기동되는 도메인을 파악하여 불필요한 셀 삽입 방지.

- 도메인 경계 근처에 아이솔레이션 셀을 배치.

12.2.2 출력 아이솔레이션과 입력 아이솔레이션

- Output Isolation (출력 아이솔레이션): 적은 셀이 필요하고 제어가 간단하지만 맞춤형 셀이 필요합니다.

- Input Isolation (입력 아이솔레이션): 표준 셀을 사용하기 쉽지만 도메인마다 별도의 아이솔레이션 셀이 필요합니다.

12.2.3 Sneak DC Leakage Paths(누설 경로)

잘못 설계된 아이솔레이션 셀이 예상치 못한 누설 경로를 만들 수 있습니다. 이를 방지하기 위한 권장 사항:

- 도메인 인터페이스에서 패스-게이트(pass-gate) 논리 사용 금지.

- 인터페이스 신호를 분석하여 잠재적인 누설 경로 파악.

- 플로팅 입력을 방지하기 위해 적절한 풀업/풀다운 트랜지스터 적용.

12.3 특수 셀 - 레벨 시프터(Level Shifters)

서로 다른 전압 도메인 간 신호 전환 시 레벨 시프터가 필요합니다.

12.3.1 레벨 시프터 유형

- High-to-Low Shifter (고->저 전압 시프터): 인버터 구조로 구성되어 단순하지만 일정한 전압 초과 시 문제 발생.

- Low-to-High Shifter (저->고 전압 시프터): 고전압 도메인 입력을 위해 특수 설계된 회로 필요.

12.3.2 레이아웃 및 설계 고려사항

- 도메인 간 N-웰 분리 필요.

- 다중 셀 행 높이로 N-웰 분리를 위한 설계.

- 전력 게이팅 시 레벨 시프터에 아이솔레이션 기능 통합.

12.4 메모리(Memories)

메모리 컴파일러를 사용하여 생성된 메모리 구성은 다중 전압 및 전력 게이팅 설계를 지원해야 합니다.

12.4.1 메모리 아키텍처

- 단일 및 다중 포트 RAM.

- 성능, 면적, 전력 최적화를 위한 구성.

12.4.2 메모리 인터페이스 설계

- 인터페이스에 레벨 시프터와 클램프를 통합.

- 메모리 근처에 인터페이스 구성 요소를 배치하여 타이밍 복잡성 최소화.

12.4.3 유지 기법(Retention Techniques)

- 전력 차단 시 메모리 내용을 유지하기 위해 유지 셀 사용.

- 입력을 클램핑하여 플로팅 신호 방지.

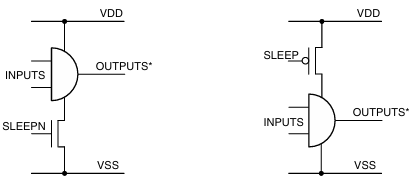

12.5 전력 게이팅 전략 및 구조(Power Gating Strategies and Structures)

전력 게이팅은 유휴 회로의 전원을 차단하여 누설 전력을 줄이는 방법입니다.

12.5.1 MT-CMOS vs. MV-CMOS

- MT-CMOS: 고-VT 스위치를 사용하여 공급 레일을 차단.

- MV-CMOS: 저-VT 스위치를 사용하며 과전압 게이트 드라이브를 요구.

12.5.2 세밀한 전력 게이팅(Fine-Grain)과 대규모 전력 게이팅(Coarse-Grain)

- Fine-Grain: 각 셀에 슬립 트랜지스터 삽입.

- 장점: 합성 용이, 짧은 기동 시간.

- 단점: 면적 증가, 특수 셀 필요.

- Coarse-Grain: 블록 단위로 전력 게이팅.

- 장점: 면적 효율성 우수.

- 단점: 전력 네트워크 설계 복잡성 증가.

권장 사항: 일반적으로 면적 효율성이 뛰어난 Coarse-Grain 방식을 권장합니다.

12.6 전력 게이팅 셀(Power Gating Cells)

전력 게이팅 셀은 전력 공급을 관리하는 역할을 하며, 헤더와 푸터 스위치로 구분됩니다.

- Footer Switches (NMOS): 전도 효율이 뛰어나며 주로 사용됩니다.

- Header Switches (PMOS): VDD 레일과의 통합이 간단합니다.

설계 고려사항

- 병렬 트랜지스터 배열로 전류 용량 향상.

- 기동 시 인러시(in-rush) 전류를 관리하기 위한 단계적 활성화 적용.

12.7 전력 게이팅 표준 셀 라이브러리

전력 게이팅 설계에서는 전력 스위치의 IR 드롭으로 인한 타이밍 변화를 고려해야 합니다.

- 초기 합성 시 과도한 제약을 설정하여 타이밍 문제 방지.

- IR 전압 드롭을 포함한 타이밍 라이브러리 사용.

실무 팁:

- 전력 게이팅 설계에서는 일반적으로 5~10% 성능 감소를 예상해야 합니다.

- 정적 및 동적 IR 드롭 분석을 철저히 수행하십시오.

이 가이드는 저전력, 다중 전압, 전력 게이팅 설계를 위한 표준 셀 라이브러리와 메모리 요구사항을 초보자도 이해하기 쉽게 자세히 설명합니다. 최적의 성능과 최소 전력 소비를 달성하려면 라이브러리 선택, 아이솔레이션 기법, 메모리 구성 및 전력 게이팅 전략을 신중히 고려해야 합니다.

"Standard Cell Library"와 "Special Cell Library"는 설계 목적과 특성에 따라 구분됩니다. 그 이유를 설명하면 다음과 같습니다:

1. Standard Cell Library(표준 셀 라이브러리)

- 정의: 대부분의 디지털 회로 설계에 공통적으로 사용되는 기본적인 셀 집합입니다.

- 포함된 셀: NAND, NOR, AND, OR, XOR, 플립플롭(FF), 레지스터, 버퍼, 인버터 등.

- 특징:

- 규격화된 크기와 인터페이스(footprint)를 가짐.

- 일반적인 디지털 로직 설계에 최적화.

- EDA 툴을 통해 자동 배치·배선(PnR, Place and Route)이 가능함.

- 역할:

- 설계자가 기본 로직 기능을 구현할 때 주로 사용.

- 성능, 전력, 면적(PPA)의 균형을 맞추기 위해 다양한 셀 크기와 속성을 제공.

- 일반적으로 프로세스 노드에 맞춰 사전에 제조업체에서 공급함.

👉 비유: 마치 블록 장난감 세트에서 가장 많이 사용하는 표준 블록들.

2. Special Cell Library(특수 셀 라이브러리)

- 정의: 특정 저전력 기능이나 인터페이스를 지원하기 위해 특별히 설계된 셀 집합.

- 포함된 셀: Isolation cells, Level shifters, Retention registers, Power switches(헤더/푸터), ESD protection cells 등.

- 특징:

- 전력 도메인 간 신호 전환, 절전 모드 데이터 유지, 전력 게이팅 기능을 제공.

- 항상 켜져 있는(always-on) 회로, 다중 전압(multi-voltage) 환경, 온칩 메모리와의 인터페이스를 위한 맞춤 설계.

- 일반 표준 셀과 다르게 특정 위치와 기능이 설계에 강제됨.

- 역할:

- 전력 관리(예: DVFS, 전력 게이팅)와 신호 무결성(아이솔레이션, 레벨 시프트)을 위한 필수 셀 제공.

- 메모리 전력 관리(메모리 리텐션)와 인터페이스 보호(ESD protection) 기능 수행.

👉 비유: 기본 블록이 아닌, 기둥이나 다리 같은 특수 구조물을 위한 맞춤형 블록.

3. 왜 구분하는가?

- 재사용성(Reusability):

- 표준 셀은 다양한 디자인에 공통적으로 재사용되기 때문에 효율적이고 비용 효과적입니다.

- 특수 셀은 특정 설계 요구를 충족하기 위해 필요할 때만 사용됩니다.

- EDA 툴의 최적화:

- 표준 셀은 EDA 툴이 최적화 알고리즘을 적용하여 자동 배치·배선 가능.

- 특수 셀은 특정 위치(전력 도메인 경계, 메모리 주변 등)에 수동으로 배치해야 하는 경우가 많습니다.

- 전력 관리(저전력 설계):

- 저전력 설계(Low-Power Design)에서는 전력 도메인 간 전압 변환, 전력 게이팅 및 리텐션 기능이 필요합니다.

- 이를 위해 특수 셀이 반드시 필요합니다.

4. SoC Power Architect의 역할

SoC Power Architect는 전력 관리 전략을 세울 때, 표준 셀 라이브러리의 성능, 전력, 면적 특성을 분석하고, 필요한 경우 특수 셀 라이브러리를 함께 고려합니다.

- 표준 셀은 기본적인 로직 설계에 필요한 기반을 제공.

- 특수 셀은 저전력 설계, 다중 전압 지원, 전력 게이팅, 메모리 리텐션 등 설계 목표를 달성하기 위한 기능을 보완.

💡 요약:

"Standard Cell Library"는 일반적인 디지털 로직 설계에 사용되는 기본 셀 모음이고,

"Special Cell Library"는 전력 관리, 인터페이스 보호 등 특정 기능을 구현하기 위한 맞춤형 셀이 포함됩니다.

저전력 SoC 설계에서는 두 라이브러리를 적절히 선택하고 함께 사용하는 것이 필수적입니다.

'IT' 카테고리의 다른 글

| IT/AI 출판사 List (1) | 2025.02.16 |

|---|---|

| SoC Interconnect (0) | 2025.02.14 |

| Physical Standard Libraries (0) | 2025.02.14 |

| Implementing Multi-Voltage, Power Gated Designs (1) | 2025.02.14 |

| DVFS 설계 (0) | 2025.02.14 |