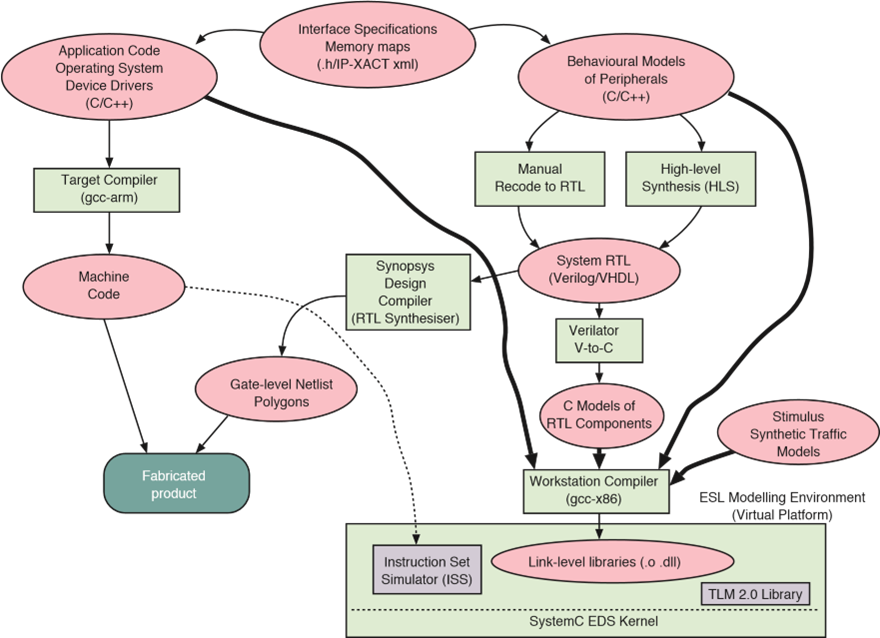

System on Chip (SoC) integrates hardware and software to communicate with the external world through various interfaces. The Electronic System Level (ESL) model of an SoC can simulate the entire system behavior in a way that allows most software to run with minimal modifications, as it would on the actual SoC. Another term for the ESL model is Virtual Platform. In some SoC design flows, creating an ESL model is the first design step. Through a process of iterative refinement, high-level components are gradually replaced with lower-level models or actual implementations. Ultimately, the whole system is implemented, but a good ESL methodology allows for any combination of interacting high- and low-level modeling styles. A common use case might involve the design existing at a high level, with the exception of one or two subsystems that require more detailed modeling to address specific design concerns.

In this context, the terms "high-level" and "low-level" refer to the abstraction level of modeling.

- High-Level: High-level models are designed with a high degree of abstraction, allowing for the quick simulation of system behavior. They are used mainly in the early stages of design to understand the big picture of the system or evaluate different architectural choices. The specific hardware implementation or cycle accuracy may be omitted or simplified, making these models useful for verifying system behavior and software interaction quickly. For example, SystemC's TLM (Transaction Level Modeling) abstracts data flow and functional behavior, representing a high-level approach.

- Low-Level: Low-level models have a lower degree of abstraction and simulate the hardware in much more detail. These are typically used later in the design process when the system's actual hardware is close to implementation. They accurately represent the system's behavior on a clock cycle basis, showing how each hardware component operates. RTL (Register Transfer Level) modeling is a common low-level modeling technique.

This section introduces the primary goals and approaches of ESL modeling. It reviews the SystemC modeling library and its transaction library (SystemC TLM), discussing how high-level models can be calibrated to provide useful insights into system performance and power consumption.

The performance of an ESL model must be good enough to run large programs in a reasonable time, typically achieving at least 1% of real system performance. ESL models are often accurate in terms of memory layout and content, but many other hardware details are ignored unless they are critical for testing. This is a key way to achieve high simulation performance.

Fundamentally, ESL models simulate the system from the power-on or reset point. Another method of applying ESL models to complex software is through checkpoints and replays. This is useful when large amounts of software need to be run before reaching a point of interest. Checkpoints are selected from points such as after booting or operating system startup. At this checkpoint, the entire state of the model is saved in a checkpoint file. While information could, in principle, be captured from the real system, the ESL model may not exactly match the real system, and small differences can occur. Additionally, installing instrumentation on the real system can be challenging, especially if it does not yet exist. Since checkpoints form the basis for multiple experiments, the time invested in creating them is offset.

To conduct experiments, the ESL model is loaded with checkpoint data, and the modeling proceeds from that point. A more detailed level of abstraction than was used during checkpoint preparation can be applied, either to the entire system or just to specific subsystems. For example, the high-level model of an I/O block could be switched to an RTL model.

The ESL description will be structured as follows:

- Modelling Abstractions

- Interconnect Modelling

- SystemC Modelling Library

- Transaction-level Modelling

- Processor Modelling with Different Levels of Abstraction

- ESL Modelling of Power, Performance, and Area

SoC(System on Chip)은 하드웨어와 소프트웨어를 결합하여 다양한 인터페이스를 통해 외부와 통신합니다. SoC의 전자 시스템 레벨(ESL) 모델은 실제 SoC에서 실행될 모든 소프트웨어를 거의 수정하지 않은 형태로 실행할 수 있는 전체 시스템 동작을 시뮬레이션할 수 있습니다. ESL 모델의 대안적인 이름은 가상 플랫폼(Virtual Platform)입니다. 일부 SoC 설계 흐름에서는 ESL 모델을 생성하는 것이 첫 번째 설계 단계입니다. 점진적인 정제 과정에서 고수준의 구성 요소를 하위 수준의 모델이나 실제 구현으로 점차 대체해 나갑니다. 궁극적으로 시스템 전체가 구현되지만, 뛰어난 ESL 방법론은 상호 작용하는 고수준 및 저수준 모델링 스타일의 임의의 조합을 가능하게 합니다. 일반적인 사용 사례로는, 현재 관심 있는 특정 설계 문제를 해결하기 위해 보다 자세한 모델링이 필요한 한두 개의 하위 시스템을 제외하고 나머지 모든 설계가 고수준 형태로 존재하는 경우가 있습니다.

여기서 "고수준"과 "저수준"이라는 용어는 모델링의 추상화 수준을 가리킵니다.

- 고수준(High-Level): 고수준 모델은 추상화 수준이 높아 시스템의 동작을 간략하고 빠르게 시뮬레이션할 수 있도록 설계된 모델입니다. 이는 주로 설계 초기 단계에서 시스템의 큰 그림을 이해하거나 다양한 아키텍처 선택지를 평가할 때 사용됩니다. 하드웨어의 세부적인 구현이나 클럭 사이클 정확성(cycle-accuracy)은 생략되거나 간소화되며, 소프트웨어와 시스템 동작을 빠르게 검증하는 데 유용합니다. 예를 들어, SystemC의 TLM(Transaction Level Modeling)은 데이터 흐름과 기능적 동작을 추상적으로 모델링하는 고수준 방법론입니다.

- 저수준(Low-Level): 저수준 모델은 추상화 수준이 낮아, 시스템의 하드웨어를 매우 세부적으로 시뮬레이션합니다. 이는 주로 설계의 후반부에서 사용되며, 실제 하드웨어 구현과 매우 유사하게 동작합니다. 클럭 사이클 단위로 정확한 동작을 모사하며, 하드웨어의 각 구성 요소가 실제로 어떻게 동작하는지를 상세하게 보여줍니다. RTL(Register Transfer Level) 모델링이 대표적인 저수준 모델링 기법입니다.

이 장에서는 ESL 모델링의 주요 목표와 접근 방식을 소개합니다. SystemC 모델링 라이브러리와 그 트랜잭션 라이브러리(SystemC TLM)를 검토하고, 고수준 모델이 성능과 전력에 대한 유용한 통찰을 제공하도록 보정(calibrate)될 수 있는 방법을 논의합니다.

ESL 모델의 성능은 대규모 프로그램을 합리적인 시간 내에 실행할 수 있을 정도로 충분히 좋아야 합니다. 이는 일반적으로 실제 시스템 성능의 최소 1%를 달성해야 함을 의미합니다. ESL 모델은 메모리 레이아웃과 내용 측면에서 정확한 것이 일반적이지만, 특별히 테스트에 중요한 하드웨어 세부 사항이 아니라면 많은 다른 하드웨어 세부 사항은 무시됩니다. 이는 높은 성능의 시뮬레이션을 달성하기 위한 주요 수단입니다.

기본적으로 ESL 모델은 시스템을 전원 공급 또는 리셋 지점에서부터 시뮬레이션합니다. 복잡한 소프트웨어에 ESL 모델을 적용하는 또 다른 방법은 체크포인트(checkpoint)와 리플레이(replay)입니다. 이는 관심 지점에 도달하기 전에 많은 양의 소프트웨어가 실행되어야 하는 경우에 유용합니다. 체크포인트는 부팅 또는 운영 체제 시작 후와 같은 지점에서 선택됩니다. 이 체크포인트에서 모델의 전체 상태가 체크포인트 파일로 저장됩니다. 원칙적으로 실제 시스템에서 정보를 캡처할 수 있지만, ESL 모델이 실제 시스템과 동일하지 않을 수 있으며 작은 차이가 발생할 수 있습니다. 게다가, 실제 시스템에 계측(instrumentation)을 설치하는 것은 어렵습니다(특히 아직 존재하지 않는 경우에는 더욱 그렇습니다). 체크포인트는 여러 실험의 기초가 되므로, 이를 생성하는 데 투자된 시간은 상쇄됩니다.

실험을 수행하기 위해 ESL 모델은 체크포인트 데이터로 로드되며, 모델링은 해당 지점에서부터 진행됩니다. 체크포인트를 준비할 때 사용했던 수준보다 더 높은 수준의 세부 사항으로 전환할 수 있으며, 이는 전체 시스템 또는 일부 하위 시스템에만 적용될 수 있습니다. 예를 들어, I/O 블록의 고수준 모델을 RTL 모델로 전환할 수 있습니다.

다음과 같은 순서로 ESL을 기술해 보려고 합니다.

1. Modelling Abstractions

2. Interconnect Modelling

3. SystemC Modelling Library

4. Transaction-level Modelling

5. Processor Modelling with Different Levels of Abstraction

6. ESL Modelling of Power, Performance and Area