DVFS 설계

주파수 및 전압 스케일링 설계

CMOS의 공급 전압을 기술별 범위 내에서 스케일링할 수 있습니다. 게이트 지연, 셋업 및 홀드 시간, 메모리 접근 시간이 제한된 범위 내에서 전압이 감소함에 따라 단조롭게 스케일링됩니다. 전압을 선형적으로 줄이면 동적 전력 소비와 누설 전력이 모두 제곱 법칙에 따라 감소합니다.

작업 부하에 따라 주파수를 줄이는 것과 함께 전압을 줄이는 전압 스케일링은 동적 전력 소비를 크게 줄일 수 있습니다. 이는 0.18µm 및 0.13µm와 같은 구형 기술 노드에서 효과적이지만, 90nm와 같은 최신 노드에서는 저누설 공정을 사용하지 않으면 효과가 떨어집니다.

그러나 전압 스케일링은 특히 휴대용 배터리 전원 장치의 경우 설계 및 구현에 복잡성을 추가합니다.

9.1 동적 전력 및 에너지

CMOS 회로의 동적 전력은 다음 공식으로 정의됩니다:

주요 포인트:

- 주파수를 줄이면 전력이 비례적으로 감소합니다.

- 전압을 줄이면 전력이 제곱 비율로 감소합니다.

- 에너지는 전력을 시간에 따라 적분한 값입니다. 주파수만 줄이면 작업 시간이 길어져 에너지 절감 효과가 제한되지만, 전압을 줄이면 에너지 절약이 가능합니다.

정적 누설 전력은 주파수가 낮아지면 작업 시간이 늘어나므로 누설이 길어져 반드시 고려해야 합니다.

9.2 전압 스케일링 접근 방식

전압 스케일링 기술에는 다음과 같은 방식이 있습니다:

- 정적 전압 스케일링(SVS): 각 블록에 고정된 전압을 제공.

- 다중 수준 전압 스케일링(MVS): 고정된 몇 가지 전압 수준 간 전환.

- 동적 전압 및 주파수 스케일링(DVFS): 작업 부하에 따라 전압과 주파수를 동적으로 변경.

- 적응형 전압 스케일링(AVS): 피드백 제어 루프를 통해 전압을 실시간으로 조정.

이 장에서는 DVFS와 AVS에 중점을 둡니다.

9.3 동적 전압 및 주파수 스케일링(DVFS)

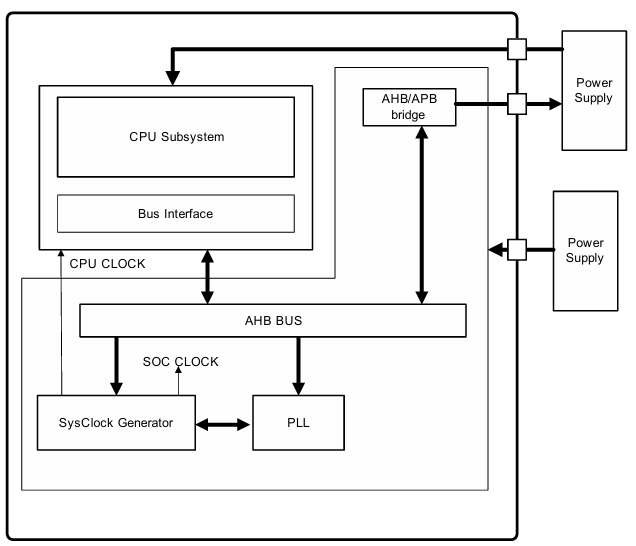

DVFS 작동 단계

- 주파수 증가

- 전력 공급 장치를 더 높은 전압으로 설정.

- 전압 안정화까지 기다림.

- 클럭 주파수를 증가.

- 주파수 감소

- 클럭 주파수를 줄임.

- 공급 전압을 낮춤.

설계 과제

- 적절한 전압-주파수 쌍 결정.

- 신뢰성 있는 타이밍 모델 확보.

- 전력 공급기 및 PLL 안정화 시간 관리.

온도 반전 현상

딥 서브마이크론 기술에서는 특정 전압 이하(약 2 × VT)에서 지연이 온도와 비선형적으로 관계됩니다. 전압 스케일링은 이 점 아래로 낮아지면 안 됩니다.

전환 시간

- 전압 변경은 전력 공급기 안정화로 인해 마이크로초에서 밀리초 단위로 오래 걸립니다.

- 주파수 변경은 분주기 값만 변경하면 빠르게 이루어질 수 있습니다.

9.4 CPU 서브시스템 설계 이슈

DVFS는 일반적으로 CPU 서브시스템에 적용됩니다. CPU와 캐시는 데이터 보존 및 인터페이스의 안정성을 위해 파티셔닝됩니다. 두 가지 설계가 있습니다:

- 통합 전압 스케일링: CPU와 캐시가 동일한 전압 레일을 공유.

- 독립적 스케일링: CPU를 독립적으로 스케일링하며, 이 경우 레벨 시프터 필요.

클럭 트리는 레벨 시프터로 인한 지연을 고려해야 합니다.

CLAMP는 전력이 차단되거나 전압 레벨이 변경될 때 신호의 안정성을 보장하기 위해 사용되는 회로 구성 요소입니다.

일반적으로 파워 게이팅 시 출력 신호를 고정 상태로 유지하거나, 전압 도메인 간 인터페이스에서 레벨 시프터와 함께 사용됩니다.

이 회로는 신호의 무효 상태를 방지하고, 전력 소모를 줄이기 위해 필수적입니다.

9.5 적응형 전압 스케일링(AVS)

AVS는 칩 내 성능 모니터를 사용하여 공정, 온도, 전압 변동을 기반으로 전압을 실시간으로 조정하는 폐루프 시스템입니다. 개방형 루프 DVFS보다 더 효율적으로 전력 소비를 최적화합니다.

🔍 구성 요소 분석

- CACHE (MEMORIES)

- 동적 전압 RAM(Dynamic Voltage RAM)과 메모리 유지 기능이 있는 캐시 메모리를 포함합니다.

- 전원 공급은 VDDRAM으로부터 제공됩니다.

- L-SHIFT/CLAMP가 인터페이스에 배치되어 있습니다.

- CPU (STD-CELL LOGIC)

- 표준 셀 로직을 포함한 CPU 블록입니다.

- 전원 공급은 VDDCPU로부터 제공됩니다.

- L-SHIFT/CLAMP가 CPU 인터페이스에 배치되어 있습니다.

- Performance Monitor (성능 모니터)

- 칩 내 전압, 온도, 프로세스 변동을 실시간으로 모니터링합니다.

- L-SHIFT/L-S/CLP를 통해 CPU와 연결됩니다.

- Power Controller (전력 컨트롤러)

- Performance Monitor로부터 신호를 받아 전력 공급기를 제어합니다.

- 필요 시 전압을 올리거나 내립니다.

- Power Supply (전원 공급 장치)

- VDDRAM 및 VDDCPU 두 가지 전압 레일을 공급합니다.

- CPU와 RAM의 전압을 다르게 관리합니다.

🔍 특징 및 동작 설명

- DVFS 동작 과정

- 성능 요구에 따라 CPU의 전압 및 주파수를 조정합니다.

- 성능이 필요하면 전압을 올리고 주파수를 증가시키며, 성능이 필요 없을 때는 전압을 낮추어 전력을 절약합니다.

- L-SHIFT와 CLAMP의 역할

- L-SHIFT (Level Shifter): 서로 다른 전압 레벨을 갖는 블록 간의 데이터 신뢰성을 보장합니다.

- CLAMP: 전력 게이팅 시 출력을 고정하여 잘못된 신호 전파를 방지합니다.

- 전력 관리 흐름

- Performance Monitor는 CPU 성능을 모니터링하여 Power Controller에 전달합니다.

- Power Controller는 Power Supply에 신호를 보내 VDDCPU 또는 VDDRAM 전압을 조정합니다.

- 메모리 유지 기능

- CPU는 power-down 상태로 진입할 수 있지만, CACHE는 memory retention 모드로 전환하여 데이터를 유지합니다.

🔍 동작 시나리오 예제

- CPU 성능 증가 요청 시

- CPU는 Performance Monitor를 통해 작업 부하 증가를 감지합니다.

- Power Controller는 Power Supply에 신호를 보내 VDDCPU 전압을 증가시킵니다.

- 전압이 안정화되면 CPU 클럭 주파수를 증가시킵니다.

- CPU 유휴 상태 시

- CPU는 유휴 상태를 인식하고 power-down 모드로 전환합니다.

- CACHE는 데이터 유지를 위해 memory retention 모드로 전환됩니다.

- Power Controller는 CPU 전압을 낮추어 전력 소비를 최소화합니다.

🧠 정리

- DVFS를 통해 필요할 때만 CPU 성능을 높이고, 유휴 시 전력을 절약합니다.

- L-SHIFT/CLAMP는 전압 레벨 전환과 파워 게이팅 시 신호 안정성을 유지합니다.

- Performance Monitor와 Power Controller는 전력 최적화를 위한 실시간 피드백 루프를 구성합니다.

이 구조는 스마트폰 AP와 같은 전력 민감형 SoC 설계에서 매우 유용합니다. 🛠️🔋💡

그림에서 CACHE(MEMORIES) 전원은 AVS(Adaptive Voltage Scaling)를 적용하지 않는 것이 명확히 보입니다.

🔍 이유 분석

- CACHE는 VDDRAM에 연결

- VDDRAM은 Dynamic Voltage RAM with memory retention을 위해 고정 전압을 사용합니다.

- 즉, 전압을 가변적으로 변경하지 않고 안정적으로 메모리를 유지할 수 있는 일정 전압을 공급합니다.

- 메모리의 특성

- SRAM 기반 CACHE는 전압을 낮추면 액세스 시간이 길어지고, 너무 낮아지면 데이터 손실 가능성이 있습니다.

- 메모리 유지(retention) 모드에서는 안정적으로 데이터를 유지하기 위해 일정 전압이 필요합니다.

- AVS의 필요성 저하

- CPU는 부하에 따라 성능을 조절하기 위해 AVS를 적용합니다.

- 그러나 CACHE는 데이터 접근 속도를 일정하게 유지하기 위해 전압을 고정합니다.

🚨 설계적 고려사항

- CPU는 AVS를 통해 성능과 전력 효율을 모두 최적화합니다.

- CACHE는 데이터 안정성을 우선시하여 고정 전압을 사용합니다.

- 고급 공정 노드에서는 메모리 전압 스케일링이 가능하나, 130nm 이하 노드에서는 전압 스케일링의 이점이 제한적입니다.

💡 결론:

CACHE는 전압을 고정(VDDRAM)하여 데이터 유지 안정성을 확보하고, CPU는 AVS로 전력을 동적으로 최적화하는 구조로 설계되어 있습니다. ✅

9.6 레벨 시프터 및 격리

멀티 전압 설계에서는 인터페이스 경계에 레벨 시프터가 필요합니다. 파워 게이팅이 적용된 경우 출력 격리가 필수적입니다. 단방향 전압 변환이 보다 단순하게 구현됩니다.

9.7 전압 스케일링 인터페이스 – 동기 타이밍에 미치는 영향

전압 변화로 클럭 트리 지연이 달라지며, 동기화 타이밍이 복잡해집니다. 이를 해결하는 방법은 다음과 같습니다:

- 비동기 인터페이스: 타이밍 관리가 단순하나 지연이 증가.

- 래치 기반 리타이밍: 클럭 도메인 간 스큐를 보정하기 위해 래치를 사용.

- 레지스터 기반 리타이밍: CPU와 버스 클럭을 정렬하여 지연 최소화.

9.8 전압 스케일링 제어

DVFS는 시스템의 성능 요구 사항을 이해하고, 주파수를 줄여도 마감 시간을 충족할 수 있는 상황을 파악해야 효과적입니다. ARM의 Intelligent Energy Manager(IEM)와 같은 정책 기반 접근 방식은 작업 수준에서 성능 요구를 분석하여 동적으로 성능을 조정합니다. DVFS 성능 제어의 정확성은 에너지 효율성과 직접 관련됩니다.