Power Gating Overview

Power Gating 개요

누설 전력 소모는 CMOS 공정 기술이 발전할수록 증가하고 있습니다. 이 누설 전력은 배터리로 구동되는 휴대용 제품뿐만 아니라 서버, 라우터, 셋톱 박스와 같은 전원이 연결된 장비에서도 점점 더 중요한 문제가 되고 있습니다.

칩의 전체 누설 전력을 줄이기 위해 사용하지 않는 블록을 꺼주는 메커니즘을 추가하는 것이 매우 중요합니다. 이러한 기법을 파워 게이팅(Power Gating)이라고 합니다.

섹션 2에서는 RTL 설계 관점에서 파워 게이팅을 설명합니다. 이 장에서는 파워 게이팅의 개요를 다루며, 이후 장에서는 RTL 수준에서 파워 게이팅을 구현하는 방법, SALT 칩에서 사용된 파워 게이팅 전략, 파워 게이팅의 아키텍처적 영향을 다룹니다. 우리의 초점은 RTL 설계자가 기술 독립적이고 이식 가능한 방식으로 파워 게이팅을 설계할 수 있도록 지원하는 것입니다.

4.1 동적 및 누설 전력 프로파일

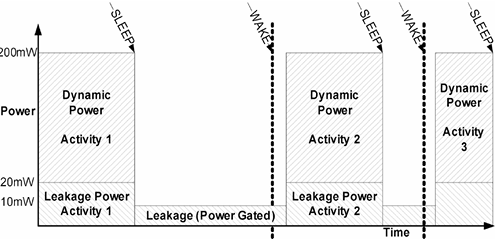

파워 게이팅의 기본 전략은 저전력 모드와 활성 모드라는 두 가지 전력 모드를 제공하는 것입니다. 목표는 성능에 미치는 영향을 최소화하면서 전력 절감을 극대화하기 위해 적절한 시점에 이 모드 간 전환을 수행하는 것입니다.

2장에서 설명한 전력 절감 기술은 설계의 기능에 영향을 주지 않으며 RTL 변경이 필요하지 않습니다. 이러한 기술은 설계 및 구현 관점에서 투명하게 처리될 수 있습니다. 그러나 파워 게이팅은 클럭 게이팅보다 더 침습적이며, 인터페이스 통신에 영향을 주고, 전력 게이팅 모드에 안전하게 진입하고 종료하기 위해 상당한 시간 지연을 추가합니다.

블록의 전원을 차단하는 작업은 장치 드라이버나 운영체제의 유휴 작업과 같은 소프트웨어에 의해 명시적으로 예약될 수 있습니다. 또는 하드웨어 타이머나 시스템 레벨 전력 관리 컨트롤러에 의해 하드웨어적으로 시작될 수 있습니다. 이 경우 설계자는 다음과 같은 아키텍처적 트레이드오프를 고려해야 합니다:

- 가능한 누설 전력 절약량

- 진입 및 종료 시 발생하는 시간 지연

- 저전력 모드 진입 및 해제 시 소모되는 에너지

- 활성/유휴 비율 및 주기적 패턴

모드 전환 이벤트에 대한 용어를 소개하겠습니다:

- SLEEP 이벤트: 저전력 모드로 진입하는 이벤트

- WAKE 이벤트: 활성 모드로 돌아오는 이벤트

활동 프로파일 예제

- 파워 게이팅이 없는 경우: 클럭 게이팅만으로 전력 절감.

- 파워 게이팅이 있는 경우: WAKE 이벤트 후 클럭 실행까지의 응답 시간이 증가.

- 실제 파워 게이팅 프로파일: 누설 전력 절약은 즉각적이지 않으며, 온도 및 기술적 한계로 인해 일정 시간이 필요.

4.2 파워 게이팅이 서브시스템에 미치는 영향

1. 캐시가 포함된 CPU 서브시스템

- 장점: 긴 유휴 시간 동안 누설 전력 절감 효과 큼.

- 단점: 인터럽트 응답 시간이 길어져 시스템 설계에 영향을 미침.

- 캐시 상태 손실 문제: 캐시를 초기화하고 다시 채우는 데 시간과 에너지 소모 발생.

- 에너지 절약 평가: 슬립/웨이크 프로파일에 따라 달라짐.

2. 주변 장치 서브시스템

- 운영체제 및 드라이버에 의해 제어 가능

- 소프트웨어에 의한 상태 저장/복구 부담

- 하드웨어 내부에 상태 저장 회로 추가 시 성능 개선 가능

3. 멀티 프로세서 CPU 클러스터

- 작업 완료 시 프로세서 전력 차단으로 누설 전력 절감

- 로컬 캐시 손실 문제 없음 (작업 완료 후 캐시 무효화)

- 워크로드에 따른 CPU 코어의 동적 전력 관리 필요

4.3 파워 게이팅 설계 원칙

파워 게이팅은 칩의 특정 블록 전원을 선택적으로 차단하는 기술입니다. 이를 통해 현재 동작 모드에서 필요하지 않은 블록의 누설 전류를 최소화할 수 있습니다.

4.3.1 파워 스위칭 방식 – 세밀한 방식(Fine Grain) vs. 거친 방식(Coarse Grain)

1) Fine Grain Power Gating

- 구성: 셀 내부에 파워 스위치를 포함.

- 특징: 전류 소모에 따라 스위치 크기 커짐.

- 장점: IR 전압 강하와 클램프 동작 특성을 쉽게 모델링 가능.

- 단점: 셀 면적 2~4배 증가로 면적 효율 저하.

2) Coarse Grain Power Gating

- 구성: 특정 블록 전체에 전력 스위칭 네트워크 적용.

- 특징: 블록의 전력 소모 패턴을 기반으로 설계.

- 장점: 셀 면적 증가가 최소화되어 설계 효율 향상.

- 단점: 인러시 전류(In-rush current) 관리 필요.

현재는 면적 대비 효율성 때문에 대부분의 설계에서 Coarse Grain Power Gating이 선호됩니다.

4.3.2 파워 게이팅 설계 시 도전 과제

- 전력 스위칭 네트워크 설계: 전류 용량과 인러시 전류 관리 필요.

- 파워 게이팅 컨트롤러 설계: 안전하고 효율적인 모드 전환 제어.

- 레지스터 선택: 상태 유지용 Retention Register 사용.

- 타이밍 및 면적 영향 최소화: 클럭 게이팅과의 상호작용 고려.

- 인터페이스 격리: 크로스바 전류 방지를 위한 Isolation Cell 추가.

- 전력 상태 검증: 시뮬레이션 및 검증 도구를 이용한 철저한 테스트.

- 제조 및 생산 테스트 전략 개발: 실제 환경에서의 안정성 확보.

파워 게이팅은 높은 누설 전력 절감 효과를 제공하지만, 설계와 검증 단계에서 신중한 접근이 필요합니다. 다음 장에서는 RTL 수준에서 파워 게이팅을 구현하는 세부 방법을 다루겠습니다.